Heterogeneous multi-core processor for tabu search scheduling algorithm

A technology of multi-core processors and scheduling algorithms, applied in electrical digital data processing, instruments, calculations, etc., can solve problems such as energy waste, high performance, loss, etc., and achieve the effect of reducing the number of sampling times and thread migration times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with the accompanying drawings and preferred embodiments.

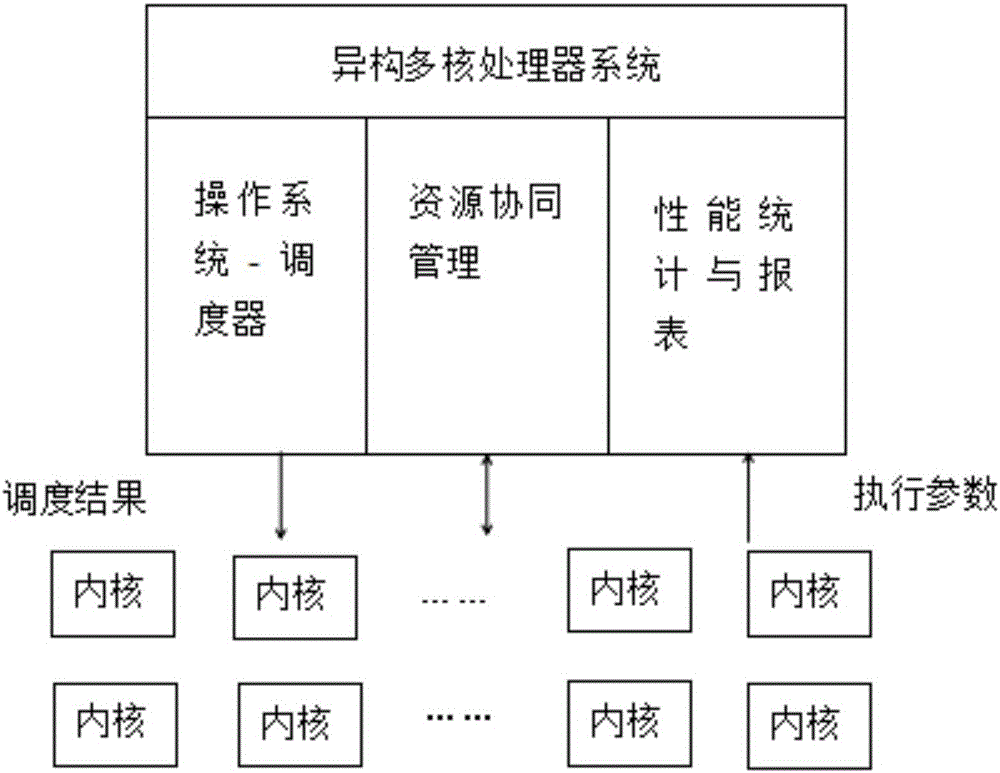

[0026] The heterogeneous multi-core processor system is realized by using multiple single cores and an upper framework. The framework structure is as follows: figure 1 shown. The bottom layer of the framework is many single cores. During the exploration cycle, the framework samples each thread, and a single core collects the performance and energy consumption parameters of the threads running on it, and then passes these parameters to the upper framework. The main functions of the upper framework include thread scheduling, resource coordination management and performance statistics. The upper-layer framework is responsible for specifying the assignment scheme for each thread in the exploration cycle of each power management time slice. It will collect and analyze the sampling data of each core, and then use the scheduling algorithm to genera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com