pll automatic test circuit and test method

An automatic test and circuit technology, applied in the direction of measuring electricity, measuring electrical variables, electronic circuit testing, etc., can solve the problems that the test results need to be observed manually, cannot be completed automatically, and cannot cover the PLL working range, so as to avoid incomplete test coverage , the effect of saving risk and workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

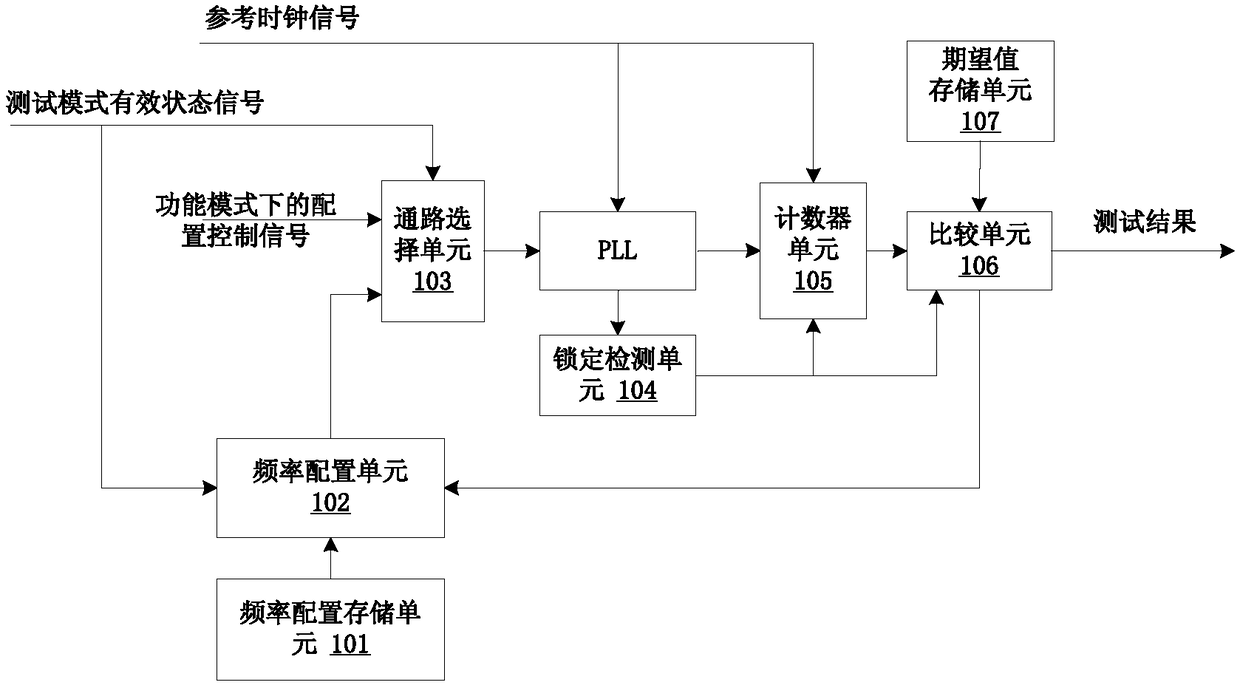

[0022] Such as figure 1 As shown, the PLL automatic test circuit of the present invention includes a frequency configuration storage unit 101, a frequency configuration unit 102, a path selection unit 103, a lock detection unit 104, a counter unit 105, a comparison unit 106 and an expected value storage unit 107; Unit 101, frequency configuration unit 102, path selection unit 103 are connected to the PLL in turn; and the frequency configuration unit 102 and path selection unit 103 are all connected to the test mode valid status bit signal; the path selection unit 103 is also connected to the Configure the control signal; the PLL, the counter unit 105, the comparison unit 106 and the expected value storage unit 107 are connected in sequence; the output of the PLL is connected to the input of the lock detection unit 104, and the output of the expected value storage unit 107 is connected to the comparison unit 106 The lock detection unit 104 is also connected to the counter unit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com