Manufacturing method for shield type differential via holes and impedance calculation method for differential via holes

A technology of differential vias and fabrication methods, applied in the formation of electrical connection of printed components, electrical components, printed circuits, etc., can solve the problems of discontinuous transmission line impedance, affecting PCB wiring density, signal integrity problems, etc., to meet the needs of high-speed signals. transmission needs, facilitates accurate design and control, resolves the effect of impedance continuity issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Below, in conjunction with accompanying drawing and specific embodiment, the present invention is described further:

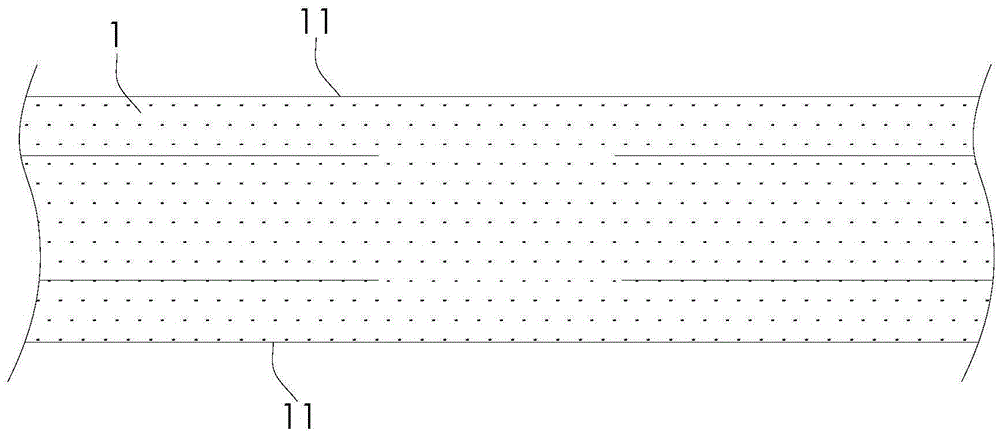

[0033] Such as Figures 1 to 6 As shown, the manufacturing method of the shielded differential via of the present invention includes: setting two reference layers 11 spaced up and down on the insulating medium layer of the PCB board 1; making ground holes 12 on the insulating medium layer of the PCB board 1 , the ground hole 12 is connected to the two reference layers 11; resin 13 is filled in the ground hole 12; a first differential transmission line 141 is arranged above and below the ground hole 12, and a second differential transmission line 141 is arranged above and below the ground hole 12. Differential transmission line 142; two differential signal vias 15 distributed at intervals are made on the PCB 1, the two differential signal vias 15 are located inside the ground hole 12, and the diameter of the differential signal via 15 is smaller than the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com