Successive approximation register analog to digital converter (SAR ADC) and switching method during analog-digital conversion thereof

An analog-to-digital converter, successive approximation technology, applied in the field of analog-to-digital converter and analog-to-digital conversion, successive approximation analog-to-digital converter and its switching during analog-to-digital conversion, can solve the waste of chip area and poor economic benefits High, increased dynamic power consumption and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] Below in conjunction with accompanying drawing of description, the present invention will be further described.

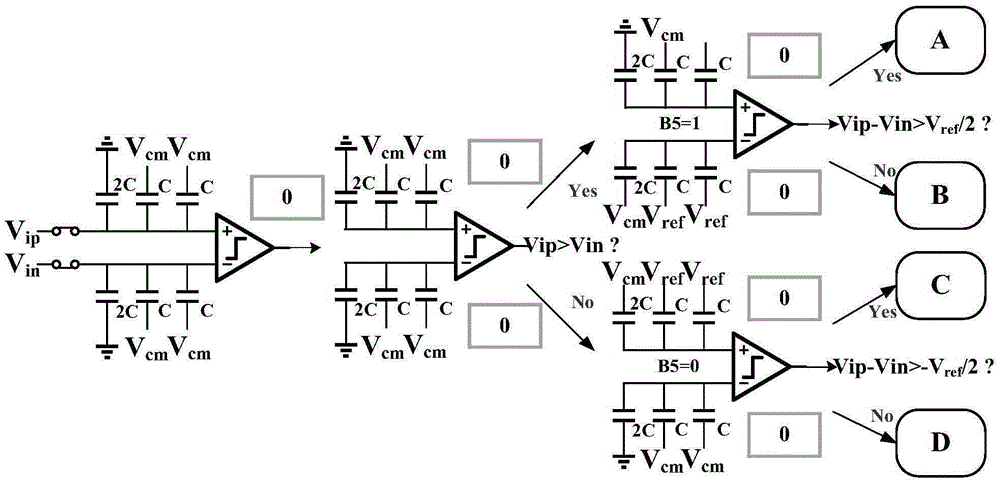

[0065] Such as figure 1 and figure 2 As shown, a successive approximation analog-to-digital converter includes a multi-reference generation circuit 1, a capacitor array digital-to-analog converter 2, a comparator 3 and a successive approximation control logic 4, and the capacitor array digital-to-analog converter 2 includes and compares The non-inverting terminal capacitor array connected to the non-inverting input terminal of the comparator 3 and the inverting terminal capacitor array connected to the inverting input terminal of the comparator 3.

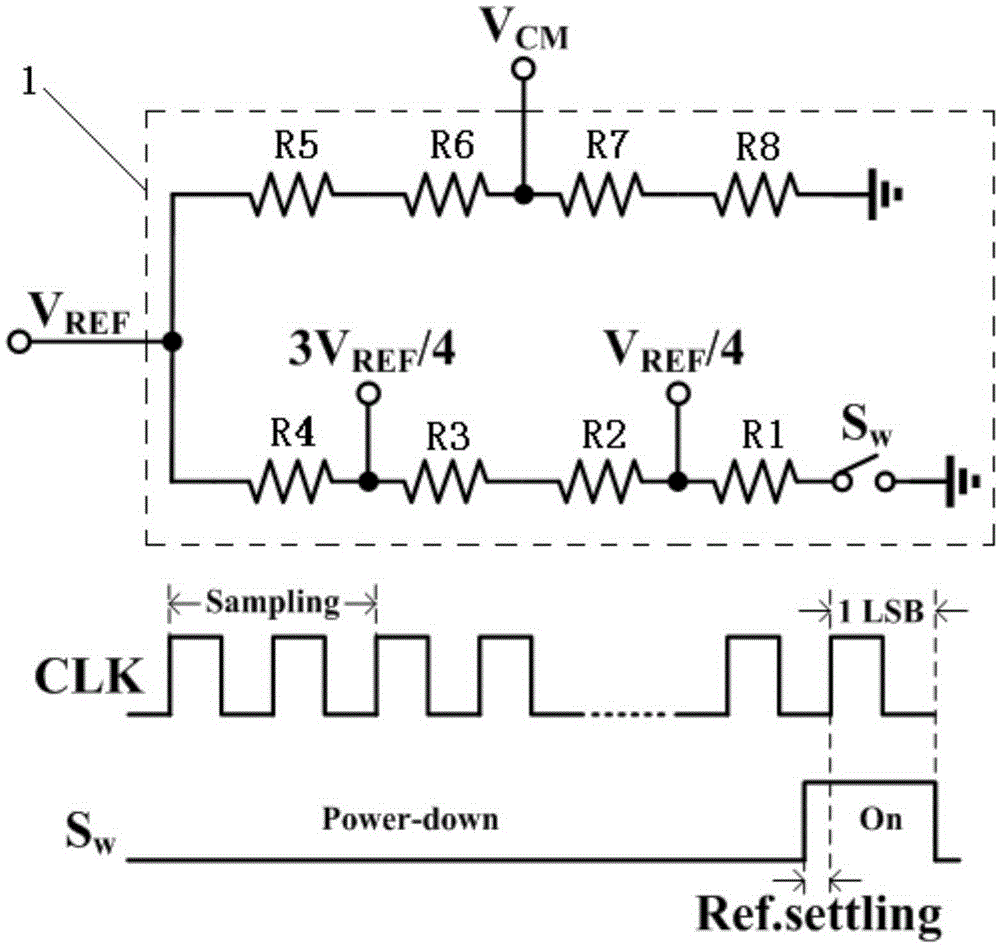

[0066] Such as figure 2 As shown, the multi-reference generating circuit 1 is used to input a reference voltage Vref to generate a common mode voltage Vcm, a quarter of the reference voltage Vref / 4 and a three-quarter reference voltage of 3Vref / 4, including a first switch SW and eight equal-resistance resist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com