Formation method of MOS transistor

A MOS transistor and furnace tube technology, applied in the field of MOS transistor formation, can solve the problems of gate dielectric layer breakdown, gate dielectric layer thickness reduction, semiconductor device performance instability, etc., and achieve growth rate and reliability improvement Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

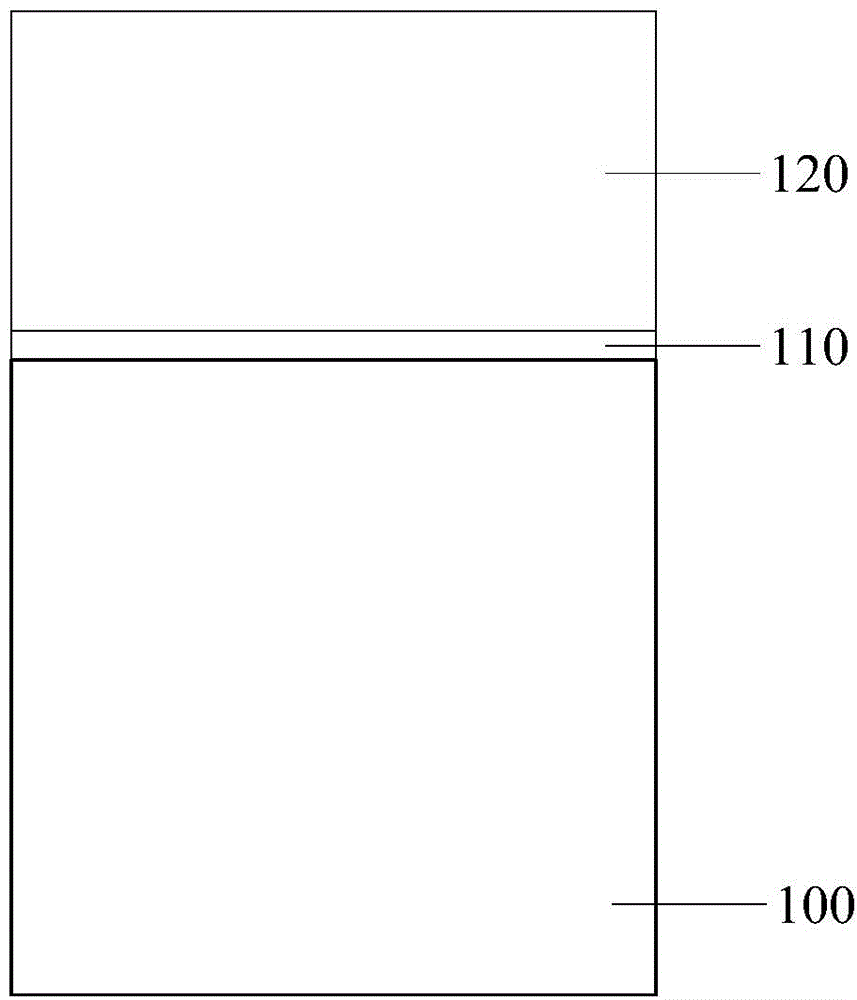

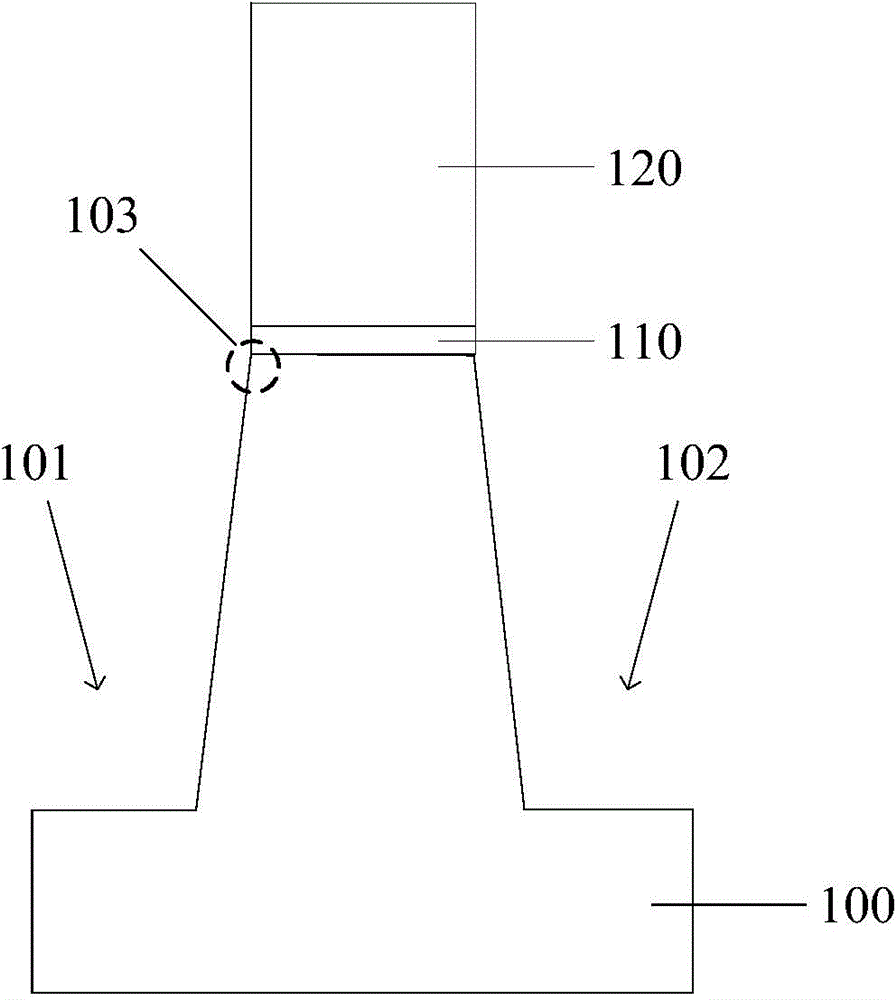

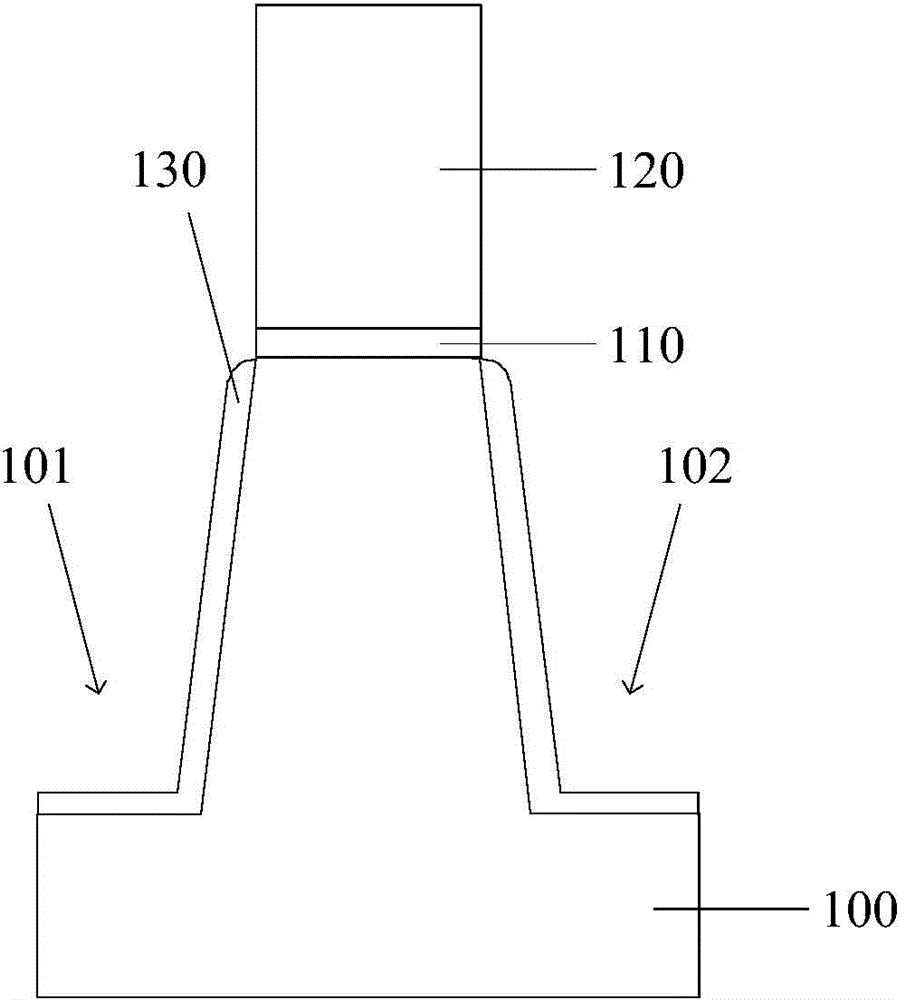

[0032] As mentioned in the background art, when the existing MOS transistor formation method forms a gate dielectric layer on the active region between adjacent shallow trenches, the thickness of the gate dielectric layer at the upper corner of the shallow trenches is generally small, resulting in a MOS transistor Time Dependent Dielectric Breakdown (TDDB) of the gate dielectric layer seriously affects the reliability of semiconductor devices, especially the reliability of non-volatile semiconductor devices.

[0033] The thickness of the gate dielectric layer at the corner on the shallow trench is relatively small, because the growth rate of the gate dielectric layer on the upper surface of the protrusion is relatively fast, while the growth rate on the corner of the shallow trench is relatively slow. The reason is that the upper surface of the active region usually has a crystal orientation, and the density of silicon atoms in this crystal orientation is relatively high, so t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com