Single event transient (SET)-resistant reinforced register suitable for SRAM type FPGA for aerospace

An anti-single event and register technology, applied in static memory, digital memory information, instruments, etc., to achieve the effect of small overall area and high anti-SET ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

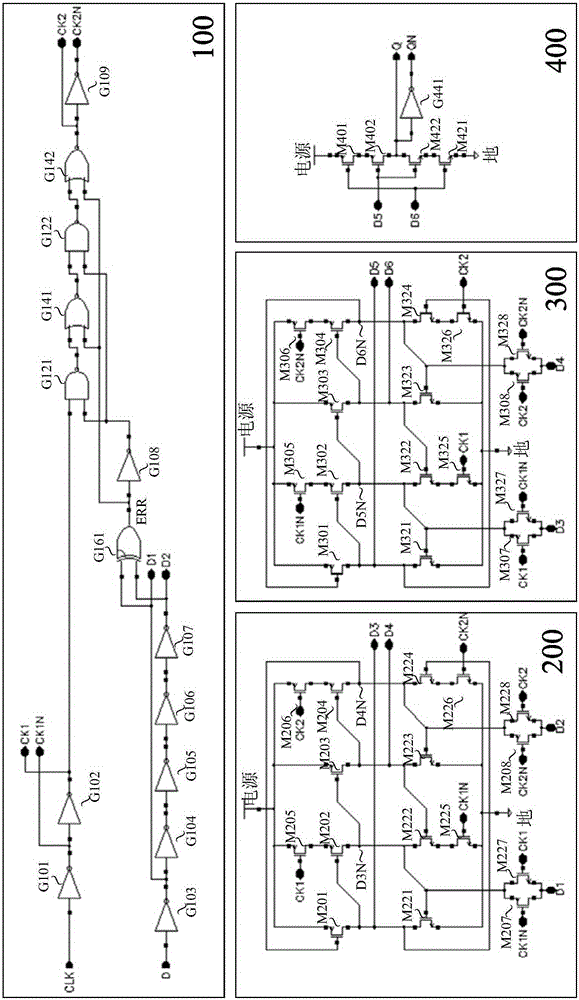

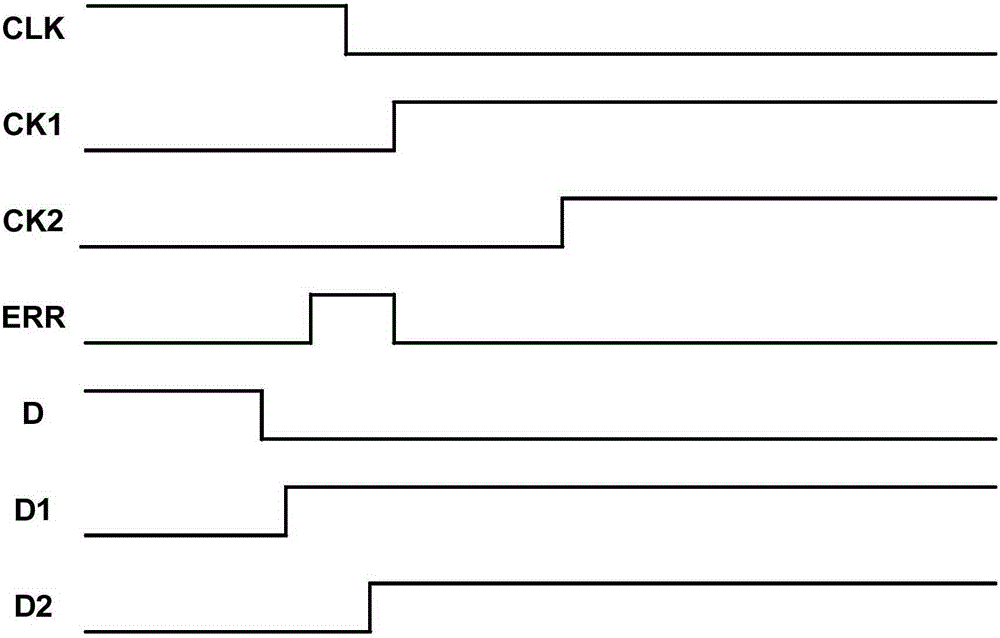

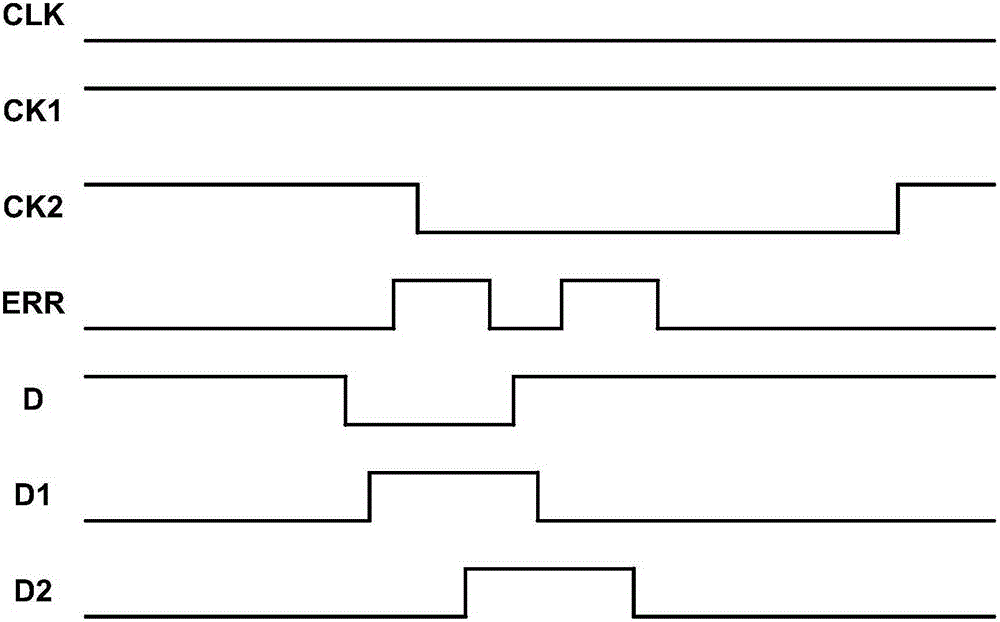

[0020] The basic idea of the present invention is to propose an anti-single event transient hardened register suitable for aerospace SRAM FPGAs. The register unit of the present invention processes the SET pulse through a new type of delay unit, so that the register has good anti-SET resistance. ability. The hardened register of the present invention is composed of four parts: internal data and clock generating circuit, master latch, and slave latch output buffer stage. The internal data and clock generation circuit uses a NAND gate and a NOR gate to form a delay chain to process the SET pulse. The master latch and the slave latch use a latch unit based on the DICE structure. The reinforced register of the present invention utilizes the inherent characteristics of the DICE unit, and uses only one delay chain to simultaneously shield the SET pulse on the clock terminal CLK and the data terminal D. Compared with the previous SET hardening register, the present invention has fe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com