Construction method for multi-layer-chip efficient X-structure obstacle-avoiding router

An obstacle avoidance router, multi-layer chip technology, applied in instruments, special data processing applications, electrical digital data processing, etc., can solve problems such as difficult problems, achieve compact logic, increase the total length of shared paths, and high efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The following combined with the attachment and specific embodiments to further explain the present invention.

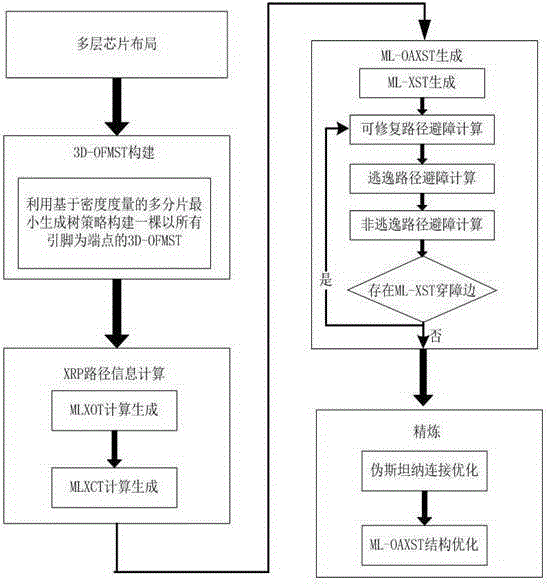

[0020] A structural method of high -efficiency X -structctric obstacle -free wiring for multi -layer chips, including the following steps:

[0021] Step S1: According to a set of pin coordinate positions, based on a fast multi-film MST constructing strategy to generate a 3D-OFMST that connects all pins, the 3D-OFMST is the infrastructure of the final ML-OAXSMT;

[0022] Step S2: The XRP information in all edges in 3D-OFMST is calculated and stored these information into two records to generate two search tables. These two search tables can provide information support for the follow-up operation of the wiring;

[0023] Step S3: Based on a quick check table, by converting each edge of 3D-OFMST into a XRP to generate a ML-XSST, and the ML-XSST will be converted into a ML-OAXST;

[0024] Step S4: Further optimize the two perspectives of ML-OAXST, to generate the final...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com