Processing method of multi-signal board level clock domain crossing

A processing method and clock domain technology, applied in the technical improvement field of cross-board clock domain, can solve problems such as non-appearance, system impact, unsatisfied data establishment and guaranteed time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The invention aims at the shortcomings and deficiencies of the general methods for eliminating the effects of burrs, and provides a method for eliminating the effects of burrs with wider applicable range and stricter restrictions than the traditional method. The invention is suitable for eliminating the influence of burrs in the FPGA design not exceeding 100MHZ.

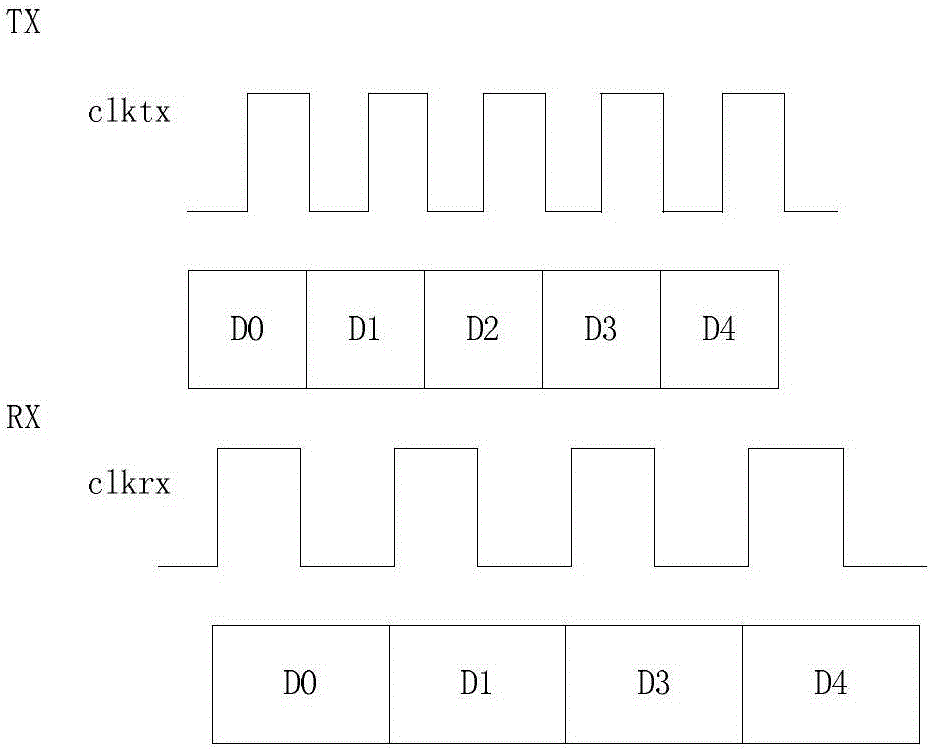

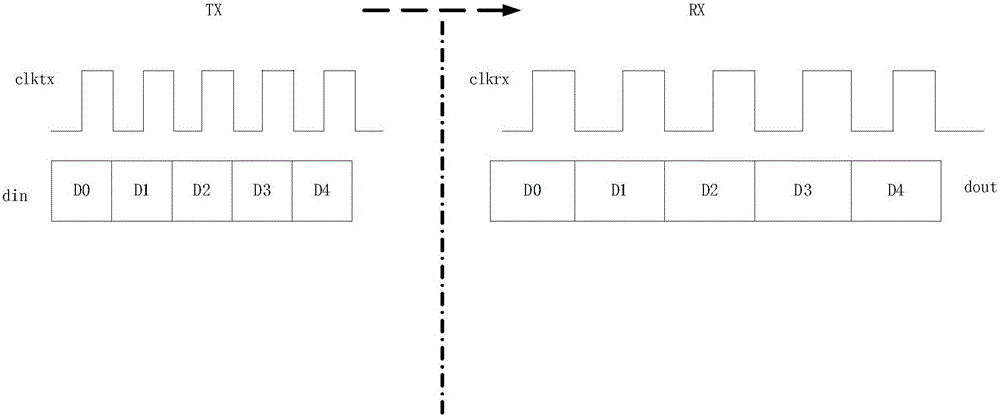

[0019] figure 1 TX is the transmitting domain, the clock reference is ClkTX, RX is the receiving domain, and the clock reference is ClkRX. ClkTX and Data[n:0] in the transmitting domain are sent to the receiving domain through the cable. The receiving domain must ensure that the received data is correct data before processing the data. In FPGA, data is usually sent and received on the rising or falling edge of the clock. Assume that the sending domain clock is clktx and the receiving domain clock is clkrx. Clktx and clkrx cannot be exactly the same clock. When receiving data at the receiving end, the data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com