8421BCD code synchronization decimal addition/subtraction counter based on reversible logic

A technology of 8421BCD and subtraction counters, which is applied in pulse counters, counting chain pulse counters, electrical components, etc., and can solve problems such as energy loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to deepen the understanding of the technical means, implementation schemes, objectives and effects achieved by the present invention, the present invention will be further elaborated below in conjunction with the accompanying drawings.

[0040] 1. Functions of reversible logic gates

[0041] At present, the commonly used reversible logic gates mainly include NOT gates, Feynman gates, Toffoli gates, Fredkin gates, and Peres gates. Their functions are as follows: figure 1 — Figure 5 shown.

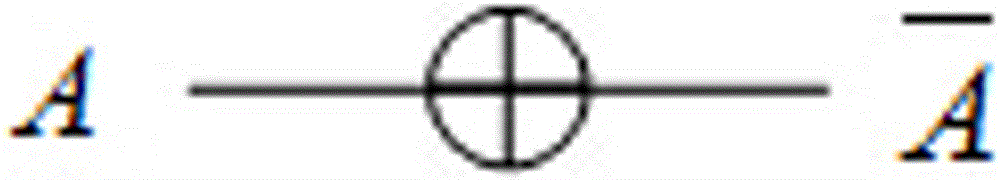

[0042] Such as figure 1 , the NOT gate has no control bit, its function is to invert the input A directly, and get

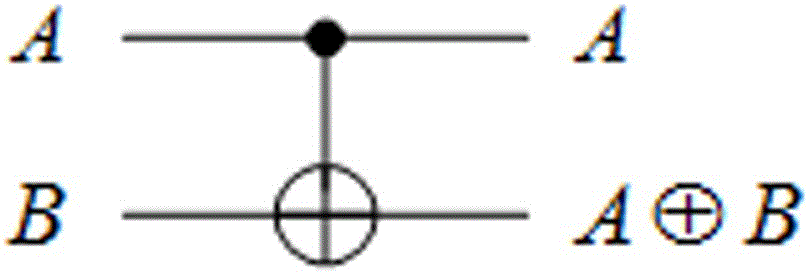

[0043] Such as figure 2 , A in the Feynman gate is the control bit, and B is the controlled bit, which can realize Operation, especially when B=0, it can realize the copy of A and avoid fan-out, and when B=1, it can realize the copy and inversion of A at the same time;

[0044] Such as image 3 , A and B in the Toffoli gate are the control bits, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com