A kind of growth method of light-emitting diode epitaxial wafer and epitaxial wafer

A technology for light emitting diodes and a growth method, which is applied to the growth method of light emitting diode epitaxial wafers and the field of epitaxial wafers, can solve the problems of limited luminous efficiency of LEDs, etc., and achieve the effects of rapid and sufficient reaction, high mobility and high luminous intensity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

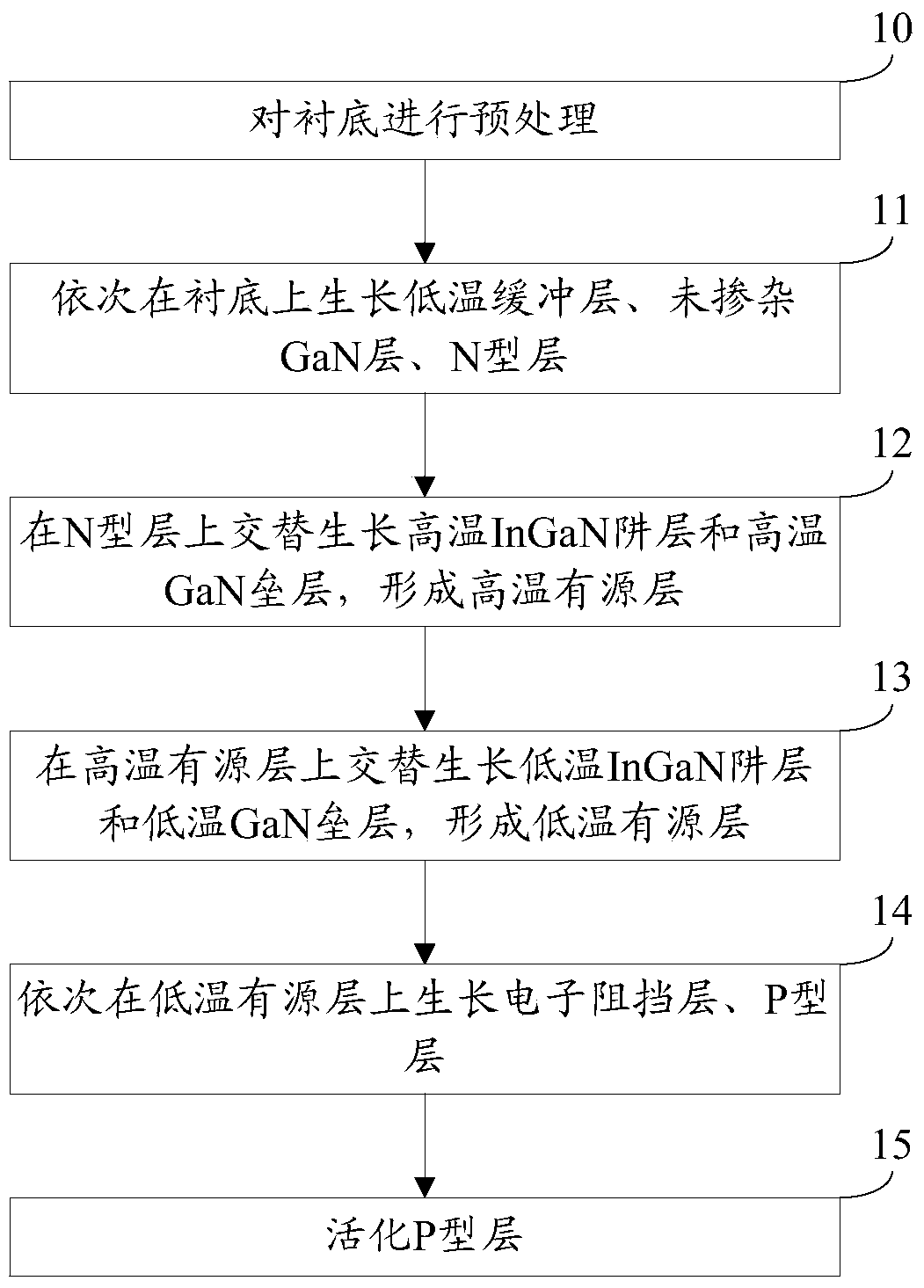

[0036] The embodiment of the present invention provides a growth method of a light emitting diode epitaxial wafer, see figure 1 , The growth method includes:

[0037] Step 10: Pre-treat the substrate.

[0038] Optionally, the substrate is sapphire.

[0039] Specifically, this step 10 may include:

[0040] Under a hydrogen atmosphere, process the substrate at a high temperature for 5-8 minutes. Among them, the temperature of the reaction chamber is 1000-1050°C, and the pressure of the reaction chamber is controlled at 200-300torr.

[0041] Step 11: Growing a low-temperature buffer layer, an undoped GaN layer, and an N-type layer on the substrate in sequence.

[0042] In this embodiment, a Veeco K465i / C4 MOCVD (Metal Organic Chemical Vapor Deposition, metal organic chemical vapor deposition) equipment is used to implement the LED epitaxial wafer growth method. Using high purity H 2 (Hydrogen) or high purity N 2 (Nitrogen) or high purity H 2 And high purity N 2 Mixed gas as carrier gas, h...

Embodiment 2

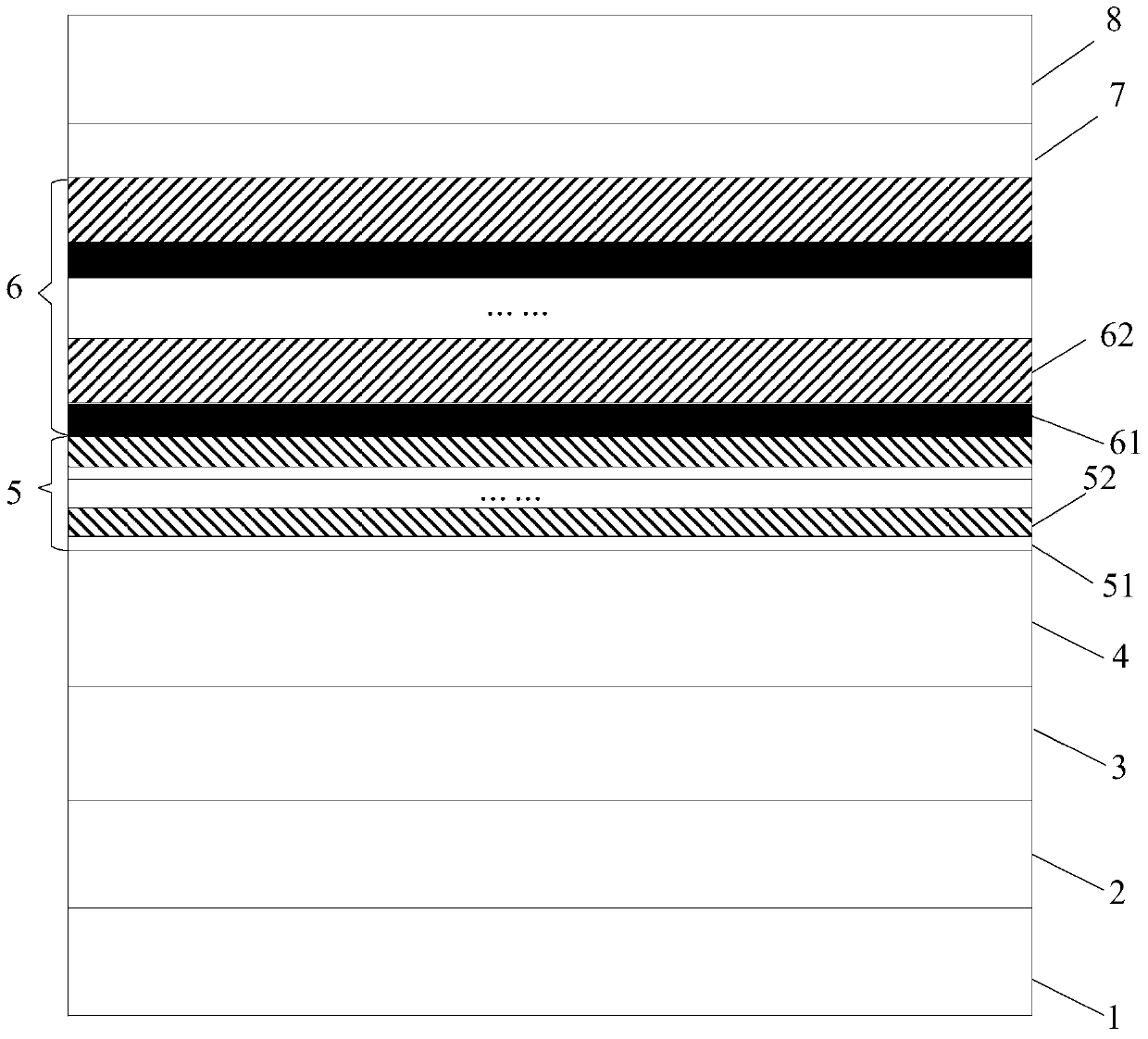

[0083] The embodiment of the present invention provides a light-emitting diode epitaxial wafer, which is obtained by using the light-emitting diode epitaxial wafer growth method provided in the first embodiment, see figure 2 The light-emitting diode epitaxial wafer includes a substrate 1, and a low-temperature buffer layer 2, an undoped GaN layer 3, an N-type layer 4, a high-temperature active layer 5, a low-temperature active layer 6, and electronic components sequentially stacked on the substrate 1. Barrier layer 7, P-type layer 8.

[0084] In this embodiment, the high-temperature active layer 5 is formed of a high-temperature InGaN well layer 51 and a high-temperature GaN barrier layer 52 that are grown alternately. The low-temperature active layer 6 is formed of a low-temperature InGaN well layer 61 and a low-temperature GaN barrier layer 62 that are alternately grown.

[0085] Among them, the growth temperature of the low temperature InGaN well layer 61 is lower than the gro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com