Flash chip and flash chip erasing method

A chip and area technology, applied in the field of memory, can solve the problems of prolonging the erasing time, increasing the erasing operation time overhead, and reducing the erasing efficiency, so as to achieve the effects of reducing overhead, improving erasing performance, and increasing erasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be described in more detail and complete below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only parts related to the present invention are shown in the drawings but not all content.

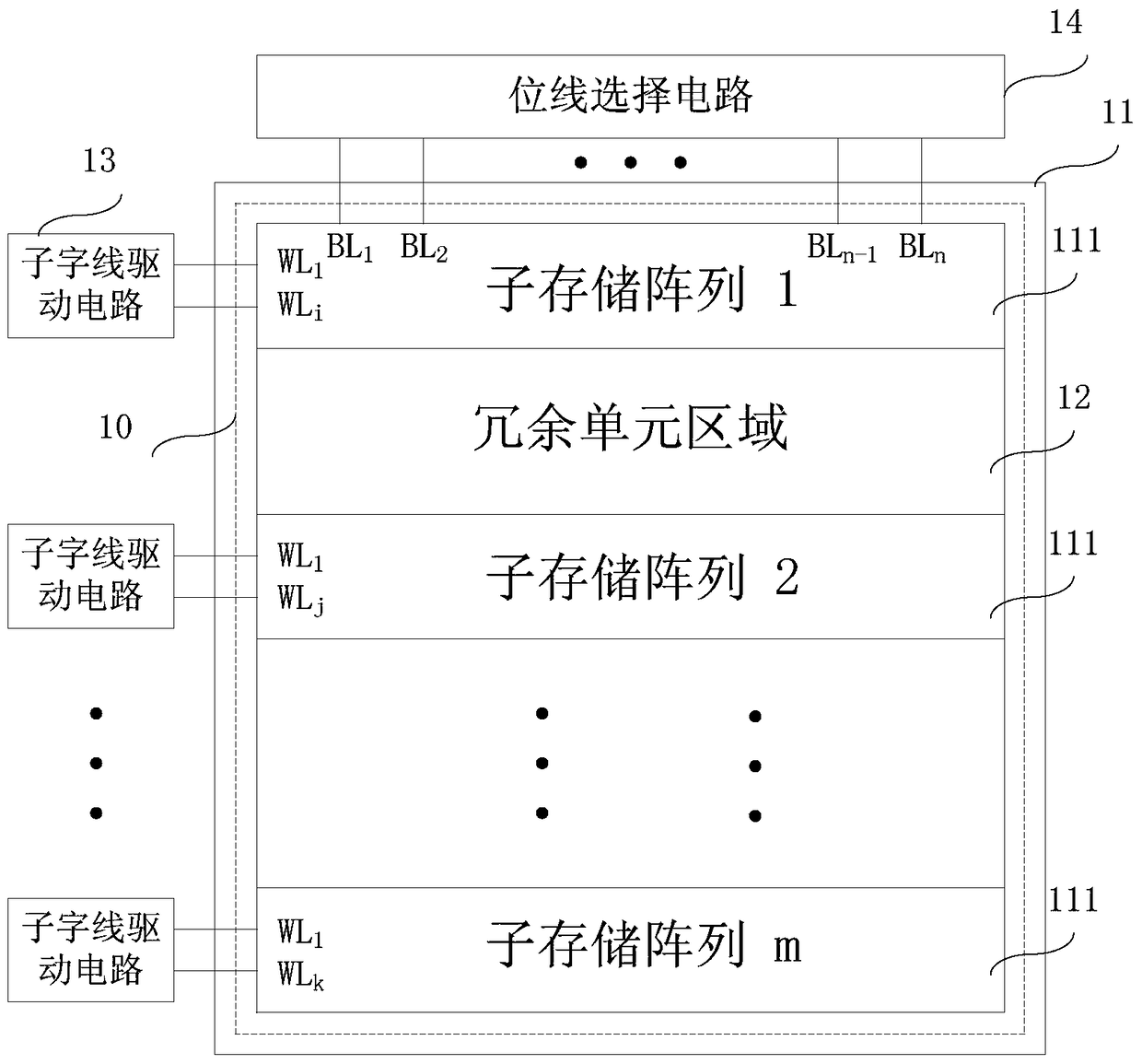

[0043] figure 1 Shown is a schematic structural diagram of the FLASH chip in Embodiment 1 of the present invention.

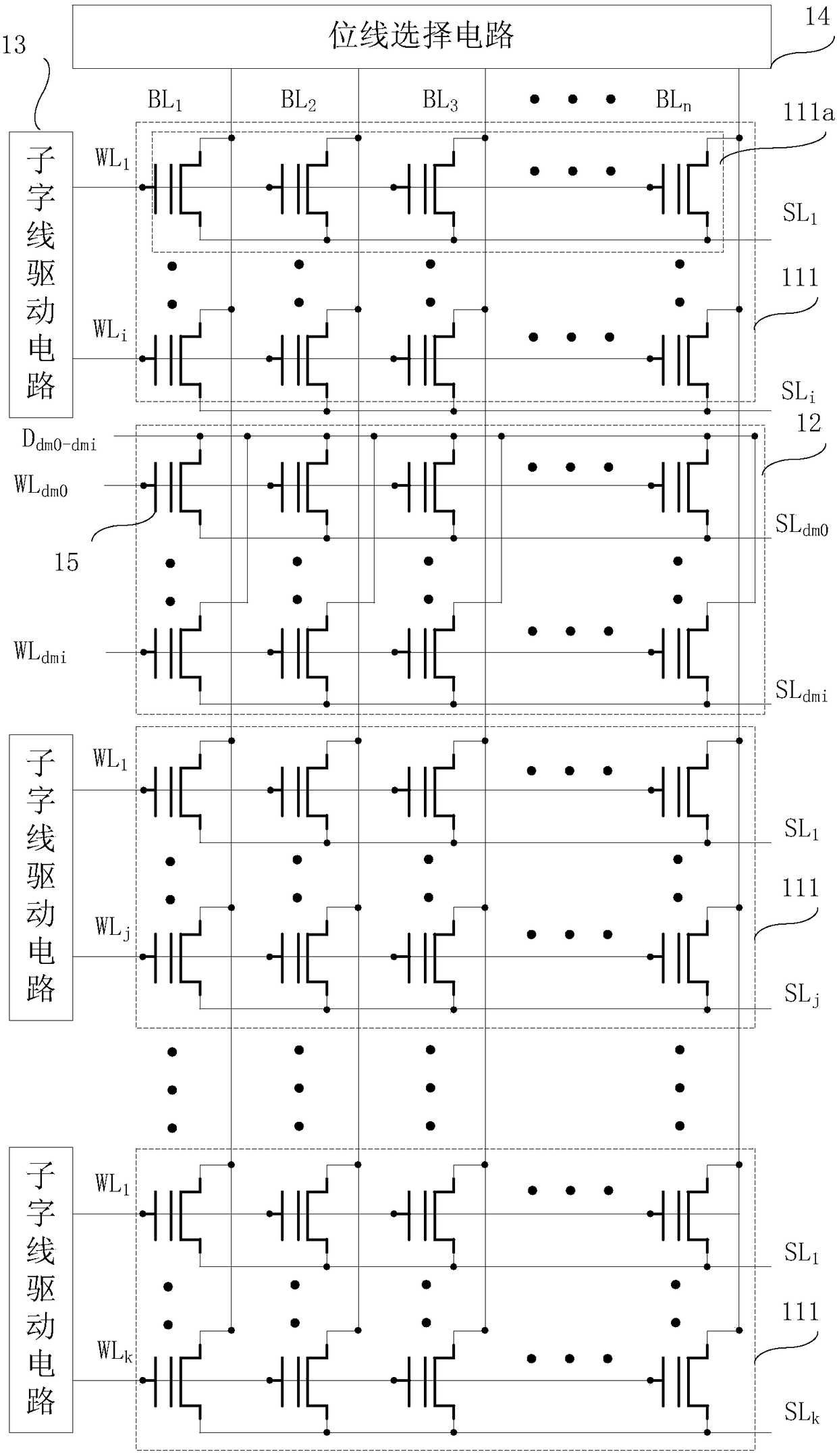

[0044] Figure 1a Shown is a schematic diagram of the distribution structure of storage units in the FLASH chip storage array in Embodiment 1 of the present invention.

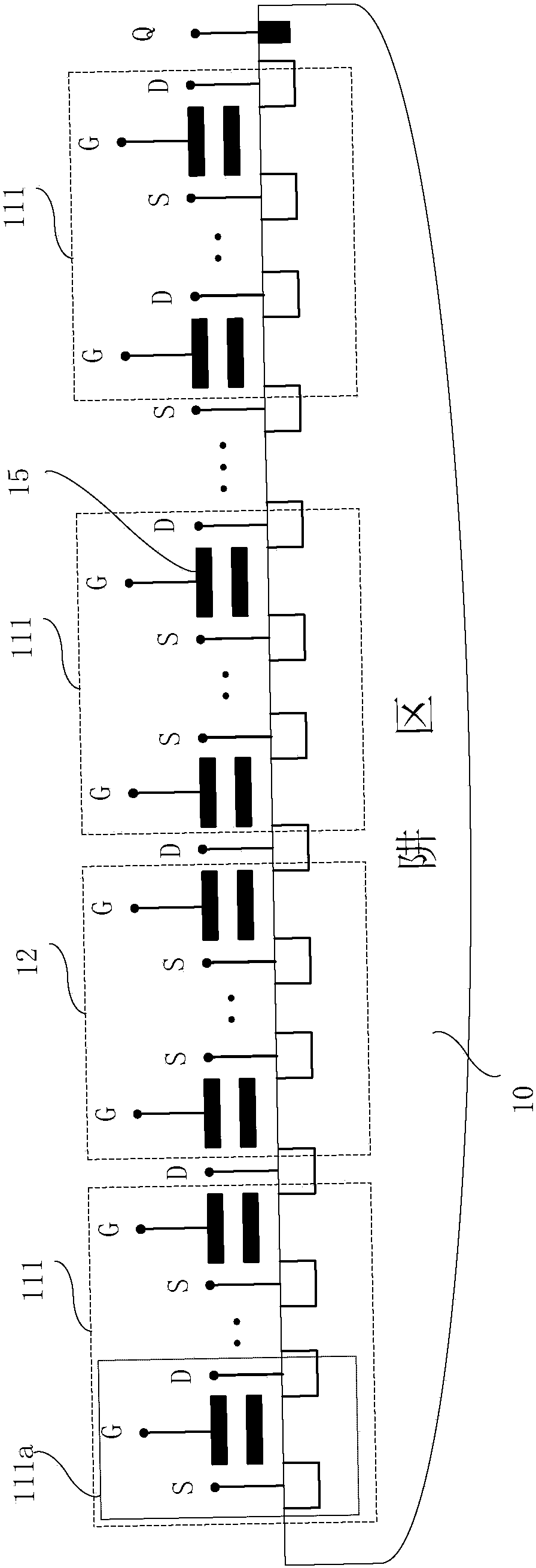

[0045] Figure 1b Shown is a schematic cross-sectional structure diagram of the distribution of memory cells in the FLASH chip memory array in Embodiment 1 of the present invention.

[0046] refer to figure 1 , Figure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com