Time relaxation-intertwined zeroing dynamic element matching encoder

A technology of dynamic component matching and time relaxation, applied in digital-to-analog converters, physical parameter compensation/prevention, etc., can solve serious power consumption, area and design complexity, mathematical derivation and specific implementation complexity, and realization complexity growth, etc. problem, to achieve the effect of ensuring the degree of randomization and dynamic characteristics, simple structure, and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

[0024] A time-relaxed interleaved return-to-zero dynamic element matching encoder according to an embodiment of the present invention will be described below with reference to the accompanying drawings.

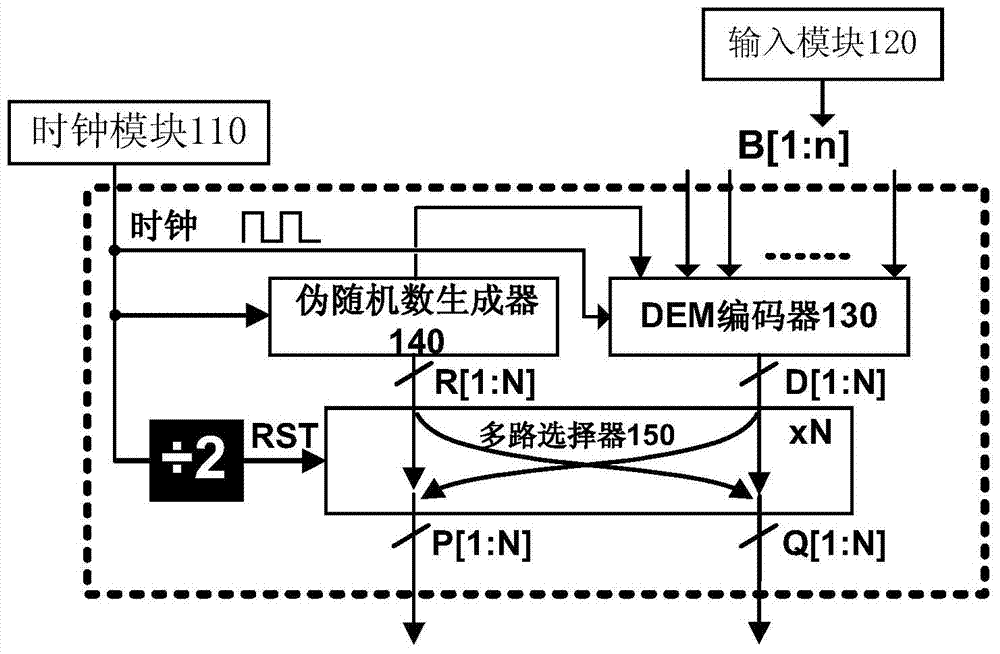

[0025] figure 2 is a structural schematic diagram of a time-relaxed interleaved return-to-zero dynamic element matching encoder according to an embodiment of the present invention. Such as figure 2 As shown, the time-relaxed interleaved return-to-zero dynamic element matching (Time-Relaxed Interleaving Return-to-Zero Dynamic Element...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com