Vertical-structure LED chip manufacturing method

A LED chip and vertical structure technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of N-type gallium nitride surface roughness, difficulty in controlling the etching depth, uneven energy, etc., to solve the problem of uneven etching depth The effect of solving the problem of uneven energy, solving the problem of energy unevenness, and reducing the damage of internal stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

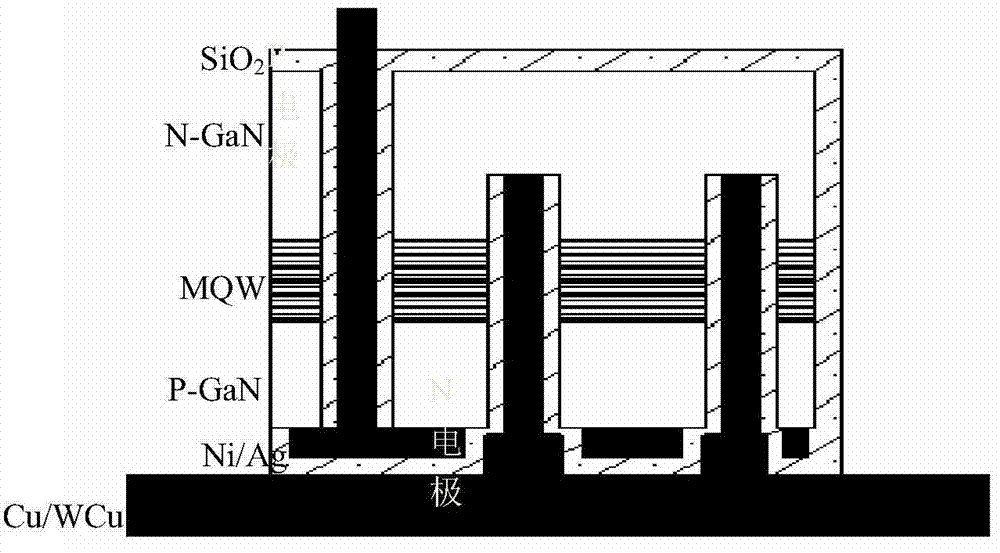

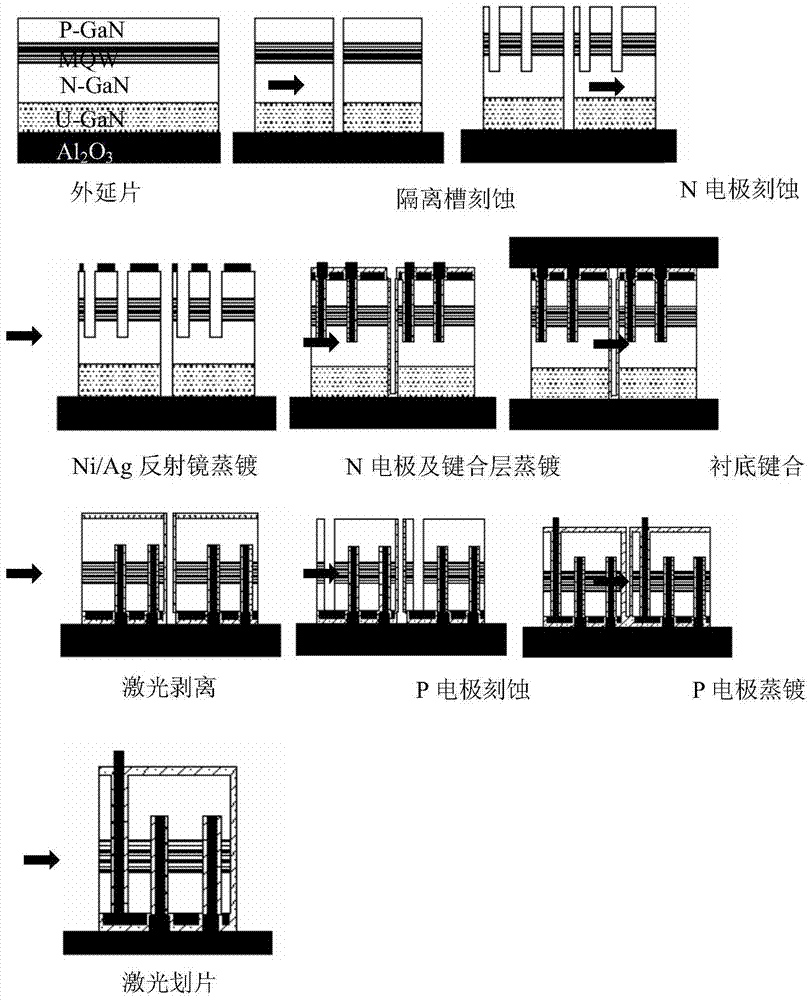

[0035] The method for preparing a vertical structure LED chip of the present invention mainly includes the following steps:

[0036] (1) Isolation groove etching: put the epitaxial wafer into the ICP etching equipment for isolation groove etching. The epitaxial wafer can be flat epitaxial wafer, PSS epitaxial wafer, secondary corroded epitaxial wafer or epitaxial wafer prepared by other methods. The etching depth is from the epitaxial wafer surface to the sapphire substrate Al 2 o 3 On the surface, silicon oxide and photoresist are used to mask the area outside the isolation groove during etching, and hot acid H is used after etching 2 SO 4 :H 3 PO 4 = Soak the 3:1 solution at 200-250°C for 3-5 minutes to form a chip isolation groove.

[0037] (2) N electrode etching and mirror evaporation: use ICP etching technology for traditional N electrode etching; use electron beam evaporation machine for mirror evaporation (Ni / Ag or Ni / Al), evaporation The edge of the covered area...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com