A method for designing server node architecture with separate high-capacity memory

A server node, high-capacity technology, applied in the direction of input/output to record carrier, etc., to achieve the effect of improving the total capacity, high capacity and performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described in conjunction with the accompanying drawings.

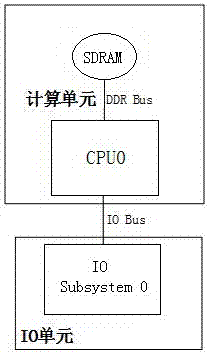

[0020] figure 1 It is a schematic diagram of the traditional server node architecture. The CPU processor and the memory sticks are placed on the same computing board, and they are interconnected through the DDR bus. Due to the limitation of the speed of the DDR bus, the distance between the processor and the memory sticks The maximum distance is limited; this architecture generally increases the memory capacity of the server by increasing the number of memory sticks.

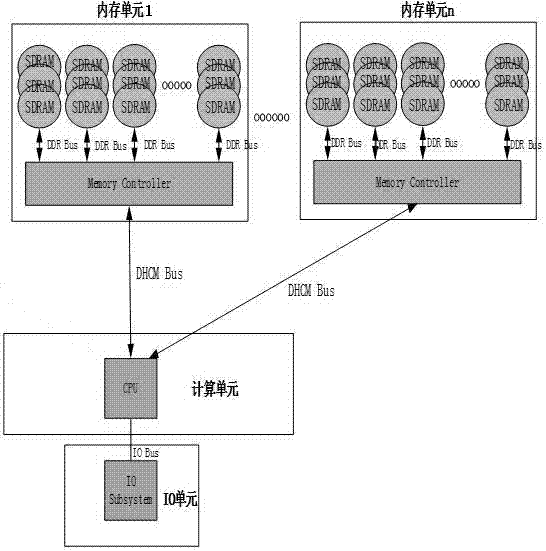

[0021] figure 2 It is a schematic diagram of the server node architecture of the present invention, wherein Memory Controller is a memory controller, DDRbus is a DDR bus, DHCM bus is a DHCM bus, and IO bus is an IO bus.

[0022] A separate high-capacity memory server node architecture, the server node includes a computing unit, a memory unit, and an IO unit;

[0023] The computing unit includes a CPU, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com