Restoration method of DRAM (Dynamic Random Access Memory) chip

A repair method and chip technology, applied in static memory, instruments, etc., can solve the problems of not being able to guarantee the robustness of chip test results, not being able to truly reflect chip designers, etc., and achieve the effect of ensuring correct access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

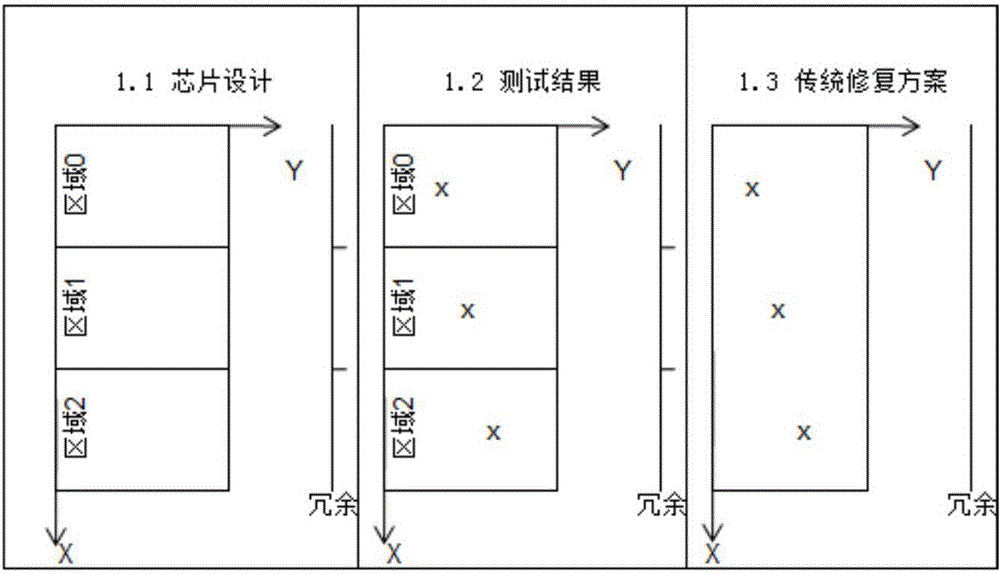

[0017] Taking the repair of DRAM chips as an example, it demonstrates the application of address boundary positioning in DRAM repair, as an example of trisection.

[0018] Such as figure 2 As shown, the repair plan provided by the chip designer is given in a, assuming that the DRAM has m (m is equal to an integer) bit X address, that is, the number of X addresses of the chip is 2 m and 2 m addresses are evenly distributed in 3 independent repair areas (area 0, area 1 and area 2), so the number of X addresses for each independent repair area is 2 m / 3, a redundant storage unit is also divided into three equal storage units according to the same rule, and each divided storage unit can independently repair the failure address of a repair area (using storage redundancy within the respective repair boundaries unit to repair the failed unit). As shown in part c, for the situation that the chip is divided into three equal parts in the X direction, on the basis of the m-bit X addr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com