VLSI (Very Large Scale Integration) circuit integrating method

A technology of large-scale integrated circuits and comprehensive methods, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems that affect the quality and quantity of netlist submission, take a long time, and module differentiation, etc. Achieve the effect of automatic processing and simple and convenient maintenance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

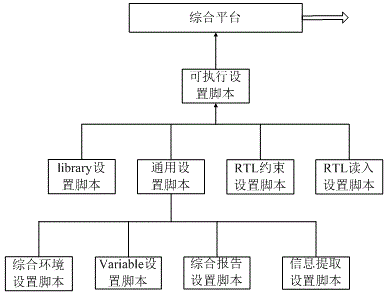

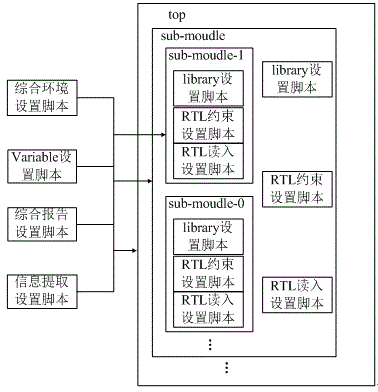

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings. The VLSI synthesis method comprises the following steps:

[0023] (1) Divide each sub-module according to logical function, boundary conditions, module size and other conditions, divide each sub-module that can be synthesized, create executable scripts, add special scripts and general scripts into executable scripts according to the order of definition and start the synthesis work; executable scripts are used to interact with the synthesis platform and manage the reading of all other setting scripts, avoiding manual reading of each setting script in different stages of synthesis. At the same time, according to the characteristics of each module, the synthesis Add specific script settings for results and work requirements, which facilitates comprehensive environmental management of different modules;

[0024] (2) According to the requirements of full-chip synthesis, de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com