PECVD coating and sintering process for protecting crystalline silicon solar cell against LID and PID

A technology of solar cells and solar cells, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of immaturity, poor compatibility of p-type production lines, restrictions on industrialization promotion, etc., and reduce the attenuation of conversion efficiency , fast and stable regeneration and recovery, and the effect of saving equipment costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

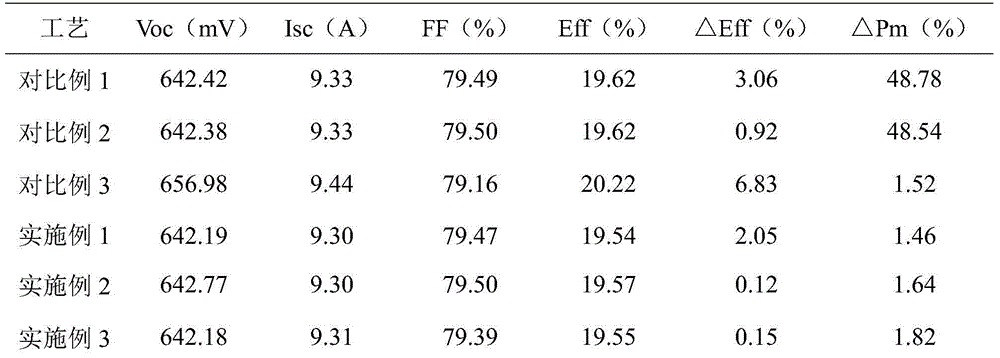

Examples

Embodiment 1

[0045] After sorting the silicon wafers, perform rough polishing in an alkaline solution (NaOH solution) to remove impurities and damaged layers, and obtain rough polished silicon wafers;

[0046] Put the roughly polished silicon wafer in an alkaline solution (NaOH solution) for texture, then wash and dry it, and the size of the texture is ≤5 μm;

[0047] The dried silicon wafer is placed in a diffusion furnace for high-temperature phosphorus diffusion, and after the PN junction is formed, the edge junction is removed by plasma etching and the PSG is removed by secondary cleaning. The square resistance of the emission area is 80ohm / squ;

[0048] Then perform PECVD coating on the silicon wafer: by deposition (passing SiH at the same time 4 and N 2 O) SiO is formed on the surface of the emission region x thin film, SiO x The film thickness is 10-20nm, the refractive index is 1.5; forming SiO x After thin film, continue to deposit to form SiN x / SiN y AR layer, SiO x Thin ...

Embodiment 2

[0051] After sorting the silicon wafers, perform rough polishing in an alkaline solution (NaOH solution) to remove impurities and damaged layers, and obtain rough polished silicon wafers;

[0052] Put the roughly polished silicon wafer in an alkaline solution (NaOH solution) for texture, then wash and dry it, and the size of the texture is ≤5 μm;

[0053] The dried silicon wafer is placed in a diffusion furnace for high-temperature phosphorus diffusion, and after the PN junction is formed, the edge junction is removed by plasma etching and the PSG is removed by secondary cleaning. The square resistance of the emission area is 80ohm / squ;

[0054] Then perform PECVD coating on the silicon wafer: by deposition (passing SiH at the same time 4 and N 2 O) SiO is formed on the surface of the emission region x thin film, SiO x The film thickness is 10-20nm, the refractive index is 1.5; forming SiO x After thin film, continue to deposit to form SiN x / SiN y AR layer, SiO x Thin ...

Embodiment 3

[0057] After sorting the silicon wafers, perform rough polishing in an alkaline solution (NaOH solution) to remove impurities and damaged layers, and obtain rough polished silicon wafers;

[0058] Put the roughly polished silicon wafer in an alkaline solution (NaOH solution) for texture, then wash and dry it, and the size of the texture is ≤5 μm;

[0059] The dried silicon wafer is placed in a diffusion furnace for high-temperature phosphorus diffusion, and after the PN junction is formed, the edge junction is removed by plasma etching and the PSG is removed by secondary cleaning. The square resistance of the emission area is 80ohm / squ;

[0060] Then perform PECVD coating on the silicon wafer: by deposition (passing SiH at the same time 4 and N 2 O) SiO is formed on the surface of the emission region x thin film, SiO x The film thickness is 10-20nm, the refractive index is 1.5; forming SiO x After thin film, continue to deposit to form SiN x / SiN y AR layer, SiO x Thin ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Film thickness | aaaaa | aaaaa |

| Layer thickness | aaaaa | aaaaa |

| Refractive index | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com