Message boundary positioning method and device oriented to plate-grade multi-channel parallel bus

A multi-channel, message technology, applied in the direction of digital transmission system, electrical components, error prevention, etc., can solve the problems of increasing the number of single-ended signal lines, increasing the number of chip board-level connections, affecting the bus bandwidth, etc., to achieve reduction Limitation of transmission frequency increase, reduction of control information load, effect of increasing effective data load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

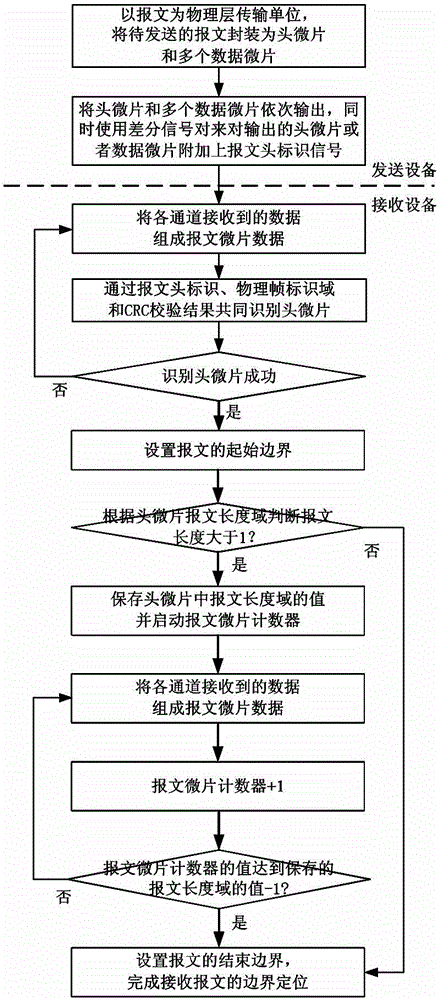

[0047] Such as figure 1 As shown, the implementation steps of the message boundary positioning method for the board-level multi-channel parallel bus in this embodiment are as follows:

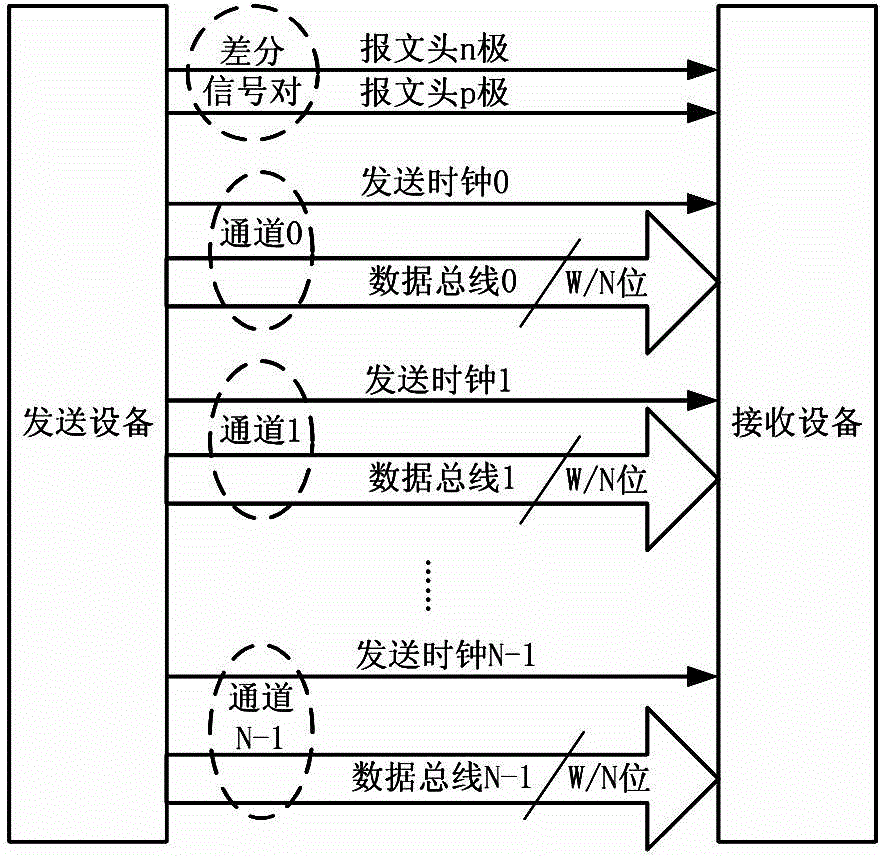

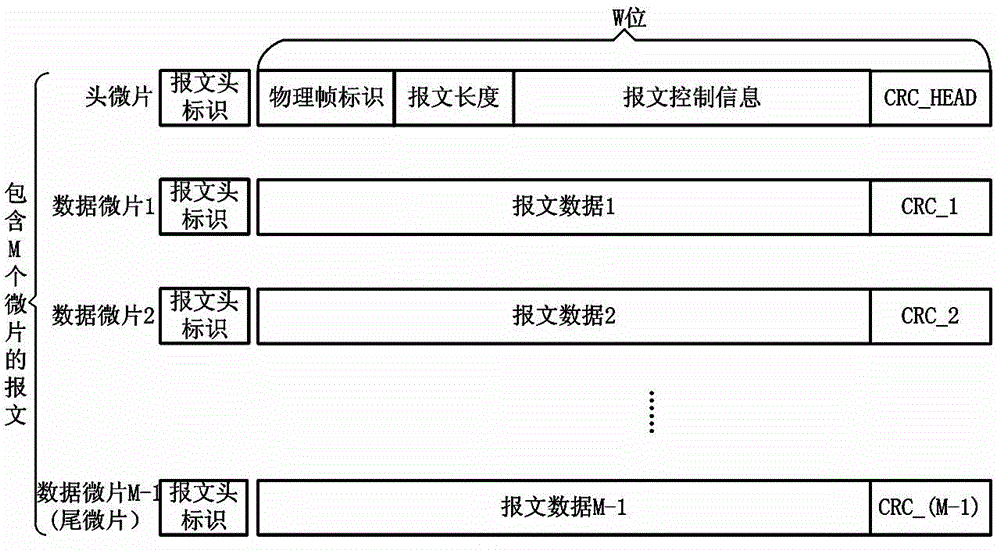

[0048] 1) Taking the message as the basic unit of bus physical layer transmission, the header flakes and multiple data flakes that constitute the message are sequentially output, and the message length field in the header flakes records the data of a complete message The number of microchips, and additionally use a differential signal pair composed of two signal lines to add a message header identification signal to the output header microchip or data microchip;

[0049] 2) The data received by each channel is composed of message microchip data, and the header microchip is identified according to the received message header identification signal and message microchip data. If the header microchip is successfully identified, the initial boundary of the message is set And start the preset messag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com