Digital phase discriminator used for GPS tame crystal oscillator

A digital phase detector and crystal oscillator technology, applied in the field of digital phase detectors, can solve the problems of slow adjustment speed of phase-locked loops, phase 2π ambiguity, phase detectors cannot directly measure frequency deviation, etc., and improve the ability to resist edge jitter , improve the locking speed, and facilitate the effect of timing design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

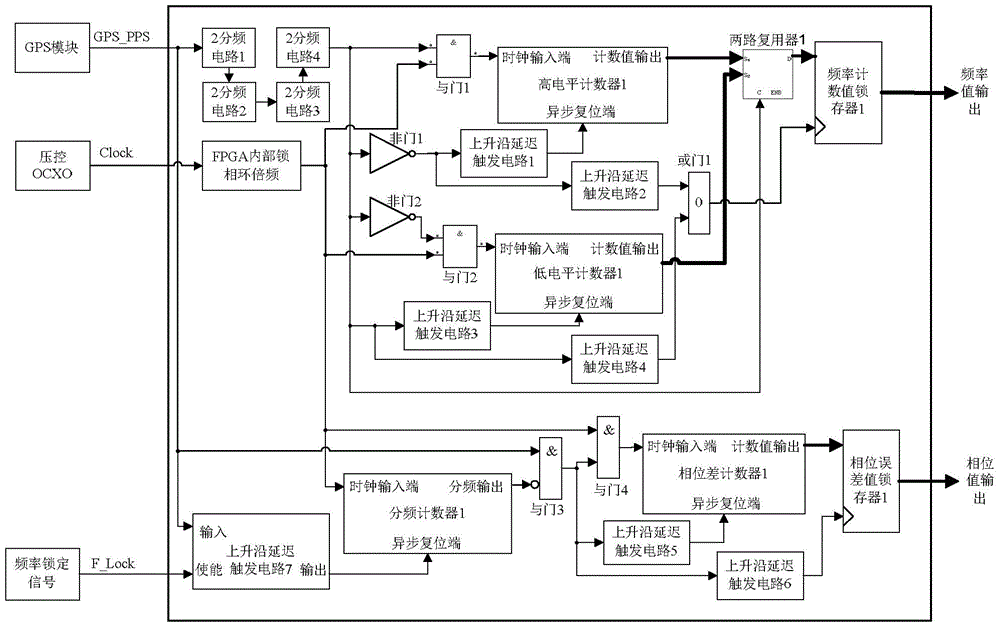

[0042] figure 1 It is the circuit structure and connection diagram of this patent. There are 3 input terminals, the first signal is the PPS signal from the GPS module, the second signal is the high-frequency clock signal from the OCXO, and the third signal is from the phase-locked loop. Outputs the coarse frequency lock status signal. There are 2 output terminals, the first one is digital frequency output, the second one is digital phase difference output.

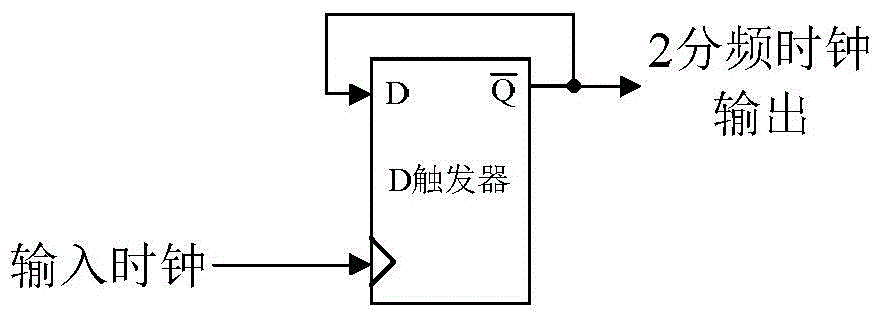

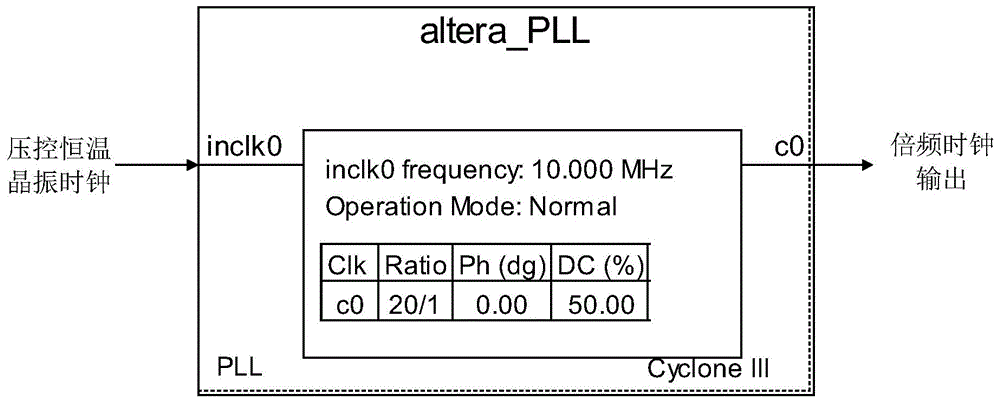

[0043] The phase detector can be divided into two parts, figure 1 The upper half is the frequency measurement circuit, and the lower half is the phase measurement circuit. The connection and work of the frequency measurement circuit are described as follows: the pin of the external input GPS_PPS signal is connected to the input terminal 1 of the frequency division circuit by 2, and the frequency division circuit plays two functions, the first function is to convert the external PPS signal into duty The ratio is 50% of...

example 1

[0052] f in example one clk =200MHz. The high-level and low-level width of the second pulse after frequency division by the 4-level 2-frequency division circuit is 8 seconds, so the capacity of the counter must be greater than 1.6×10 9 , the number of bits of high level counter 1 and low level counter 1 in example 1 is set to 32 bits. Therefore, the bit width of the frequency counting latch 1 is also 32 bits. The final frequency measurement value is output from the frequency count value latch 1, and the value in the latch is refreshed every 8 seconds, and the refresh time is the delay T after the rising edge and falling edge of the second pulse after 16 frequency division d2 long moments. When using, pay attention to reading the frequency count value latch 1 synchronously with the GPS PPS signal, and avoid the data refresh time.

[0053] The second part of the phase detector, namely figure 1 The phase error measurement circuit in the middle and lower parts realizes the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com