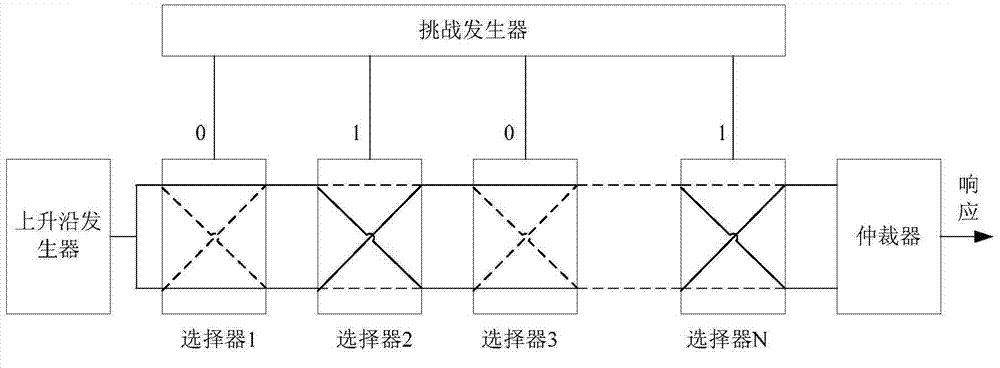

Physical unclonable function circuit structure based on double delay chains

A function circuit, double delay technology, applied in the field of physical unclonable function circuit structure based on double delay chain, can solve the problems of fixed delay difference, PUF uniqueness reduction, PUF delay deviation is not easy to balance, etc. The effect of delay difference equalization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with specific examples, but the present invention is not limited to these specific implementations. Those skilled in the art will realize that the present invention covers all alternatives, modifications and equivalents as may be included within the scope of the claims.

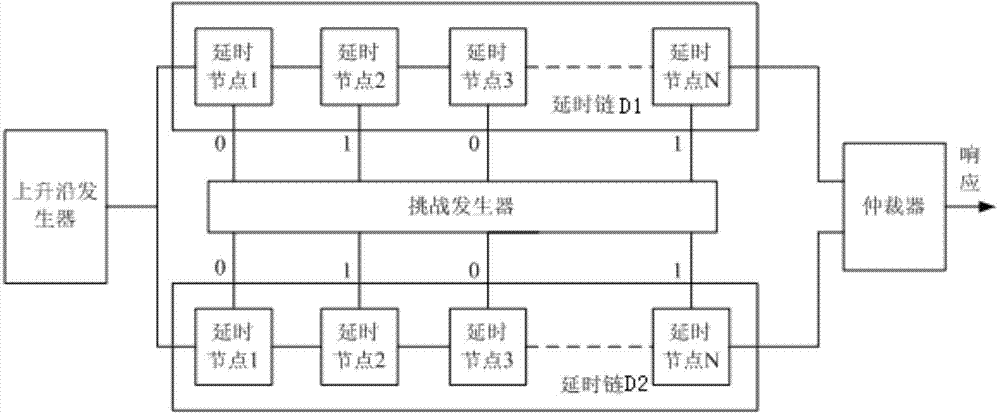

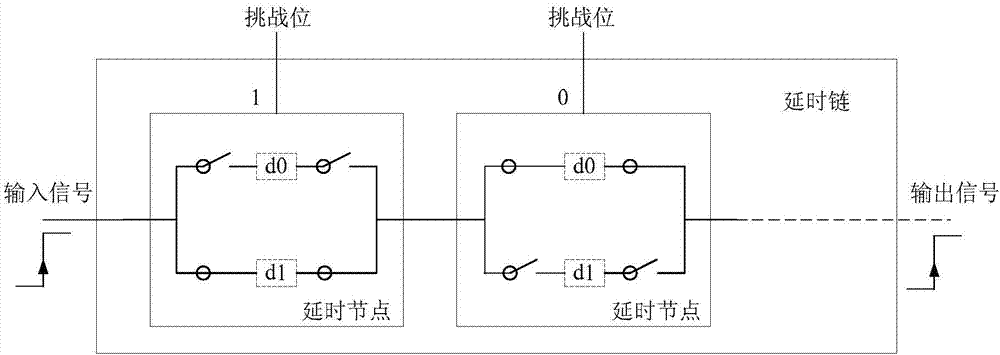

[0032] refer to figure 2 , a physical unclonable function circuit structure based on double delay chains, including a rising edge generator, a challenge generator, a delay chain D1, a delay chain D2 and an arbitrator, the signal output terminals of the rising edge generator are respectively connected to the delay The signal input ends of time chain D1 and delay chain D2 are connected, and the signal output ends of described delay chain D1 and delay chain D2 are all connected with the signal input end of arbitrator, and described delay chain D1, delay chain D2 They are all connected by N delay nodes, and each of the delay nodes is pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com