How to make through silicon vias

A manufacturing method and technology of through-silicon vias, which are applied in the manufacture of microstructure devices, processes for producing decorative surface effects, decorative arts, etc., can solve the problem of high contact resistance between pure polysilicon fillers and connecting lines, and reliability of thermal expansion coefficient devices. Reduction and other problems, to achieve high density, low contact resistance, and solve the effect of large contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] like Figure 1A to Figure 1M As shown, the present invention provides a method for manufacturing through-silicon vias, which at least includes the following steps:

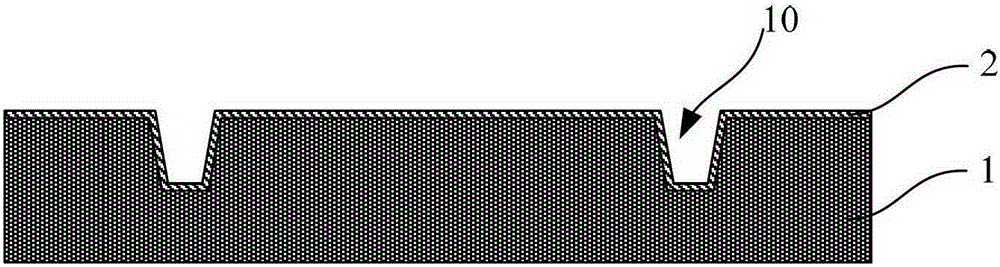

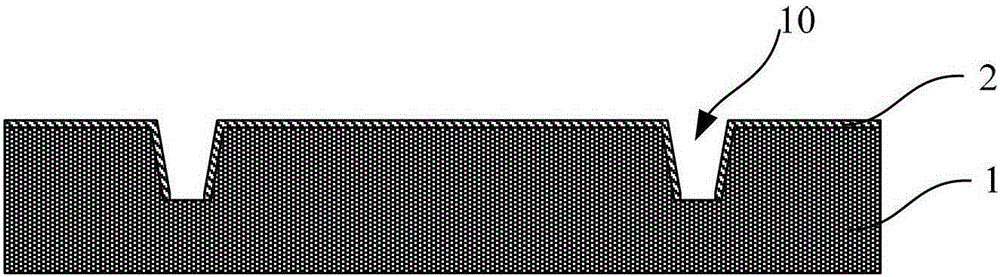

[0045] Firstly, step 1) is performed to provide a substrate 1 , and the groove 10 is formed by dry etching or wet etching at the place where the TSV is prefabricated in the substrate 1 . Wherein, the dry etching includes at least reactive ion etching (ReactiveIonEtching, RIE) or inductively coupled plasma (InductiveCoupledPlasma, ICP), and the wet etching includes at least using potassium hydroxide solution; the material of the substrate 1 is Silicon; the shape of the opening of the groove 10 is circular or square, the size of the opening is 80-150 μm, and the aspect ratio of the groove 10 ranges from 1 to 5; the angle between the side wall of the groove 10 and the opening depends on For the method of making the groove, the angle between the side wall of the groove 10 and the opening can be approximately 9...

Embodiment 2

[0059] Embodiment 2 adopts basically the same technical solution as Embodiment 1. The difference is that the manufacturing method of through-silicon vias in this embodiment 2 is applicable to the case where through-silicon vias realize the electrical connection of MEMS devices. The specific difference is reflected in step 4. ), which will be described in detail later.

[0060] like Figure 2A to Figure 2H As shown, the present invention provides a method for manufacturing through-silicon vias, and the manufacturing method at least includes:

[0061] First perform the same steps 1)~3) as in Example 1, such as Figure 2A~2D As shown, a groove 10' filled with an epitaxial layer 3' of silicon material and an insulating layer 2' formed on a side wall is made on a substrate 1'. Wherein, the groove 10' corresponds to the prefabricated TSV; the insulating layer 2' is formed on the side wall of the groove 10' but there is no insulating layer 2' at the bottom of the groove 10'; The e...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com