Method for making mask layout minimum physical rule verification file

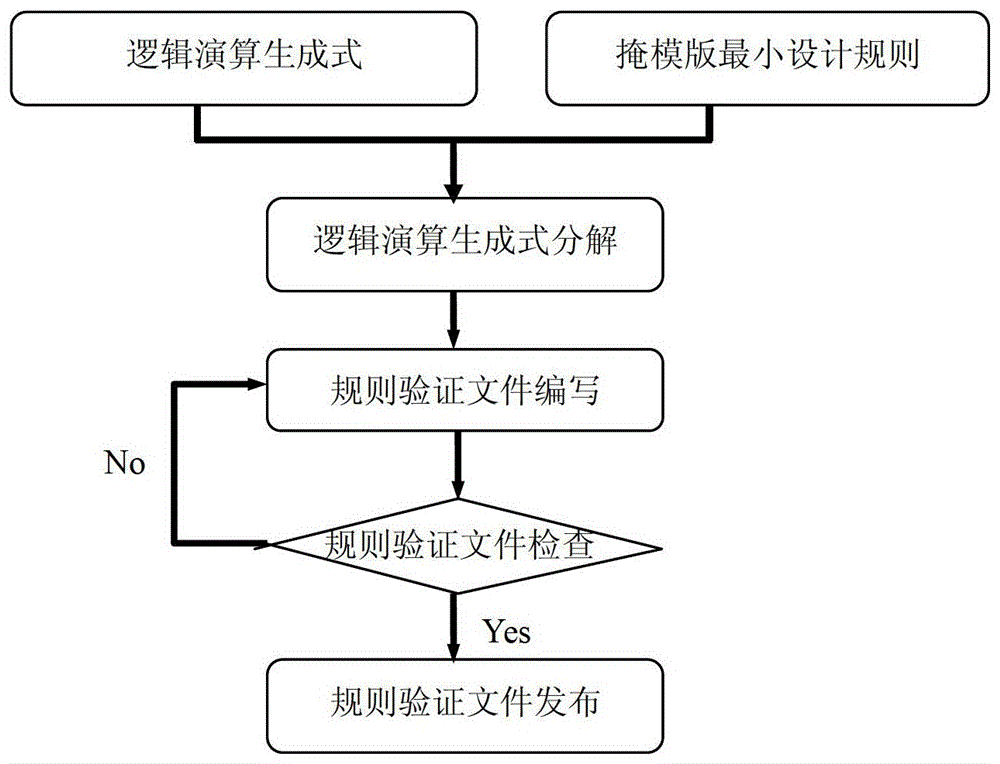

A production method and rule technology, applied in the field of production of the minimum physical rule verification file of mask layout, can solve problems such as development errors, shorten the development process, etc., and achieve the effect of eliminating hidden errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

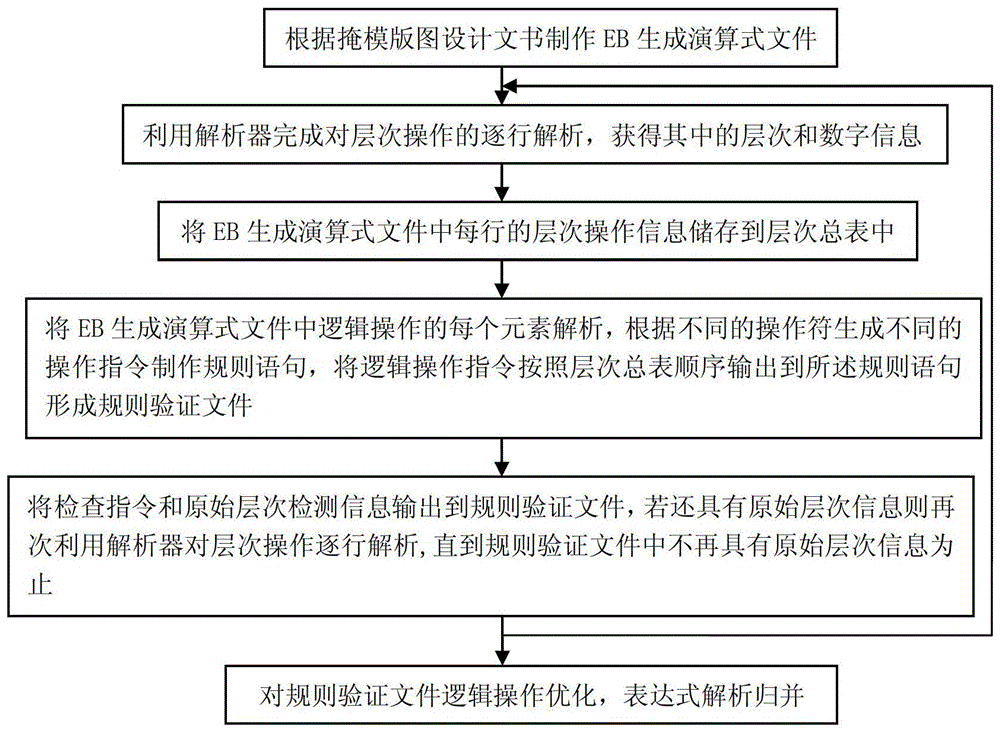

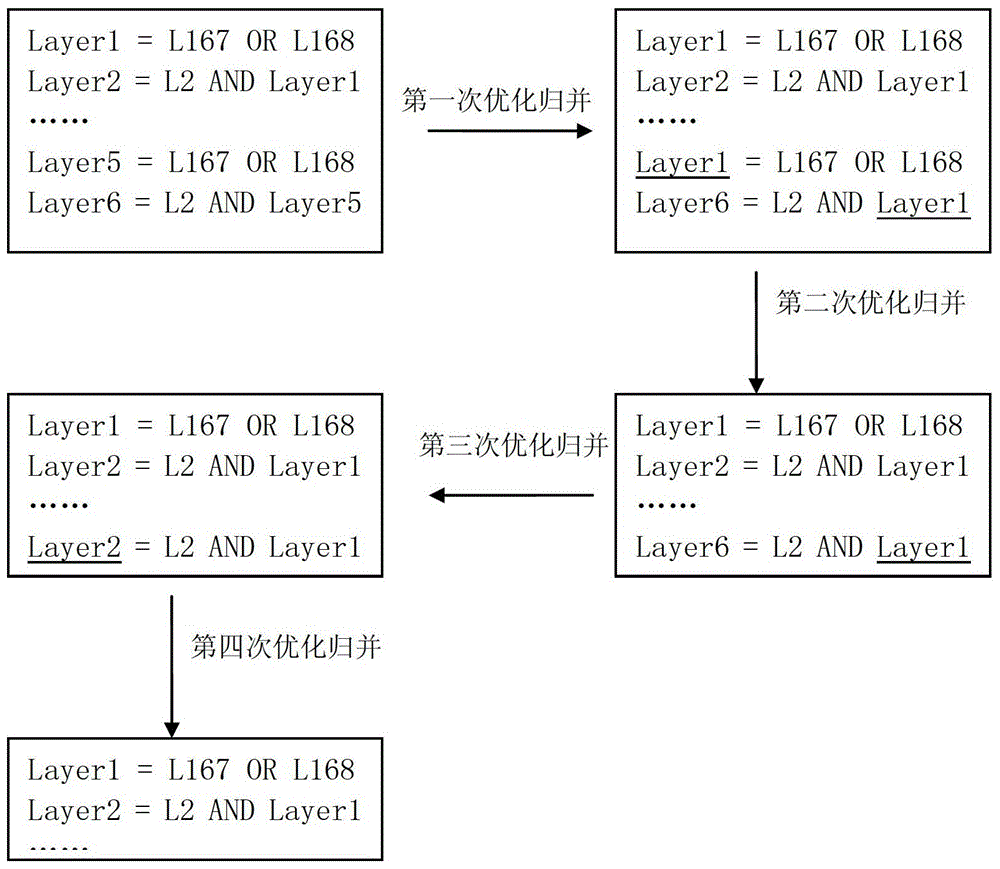

[0020] like figure 2 As shown, an embodiment of the present invention is implemented under the LINUX system, including:

[0021] 1) According to the mask layout design document, the EB generation calculation formula file is produced, and the EB generation calculation formula file provides the original hierarchical information for generating the minimum physical rule verification document of the mask layout;

[0022] The calculation formula file generated by the EB is based on the layer information (mask number, mask name, layer number, logic operation formula, line width / spacing) in the mask layout design document and uses the mask number, mask name, logic operation formula , line width, and spacing are listed in order to provide the original hierarchical information for generating the minimum physical rule verification file of the mask layout;

[0023] The following is the content of an embodiment of the calculation formula file generated by EB:

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com