Adjustment method for parameters of chips on wafer

A chip and parameter technology, which is applied in the field of chip parameter adjustment on the wafer, can solve the problems of increased test time, inability to meet mass production, and different chips, and achieve the effect of shortening the test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

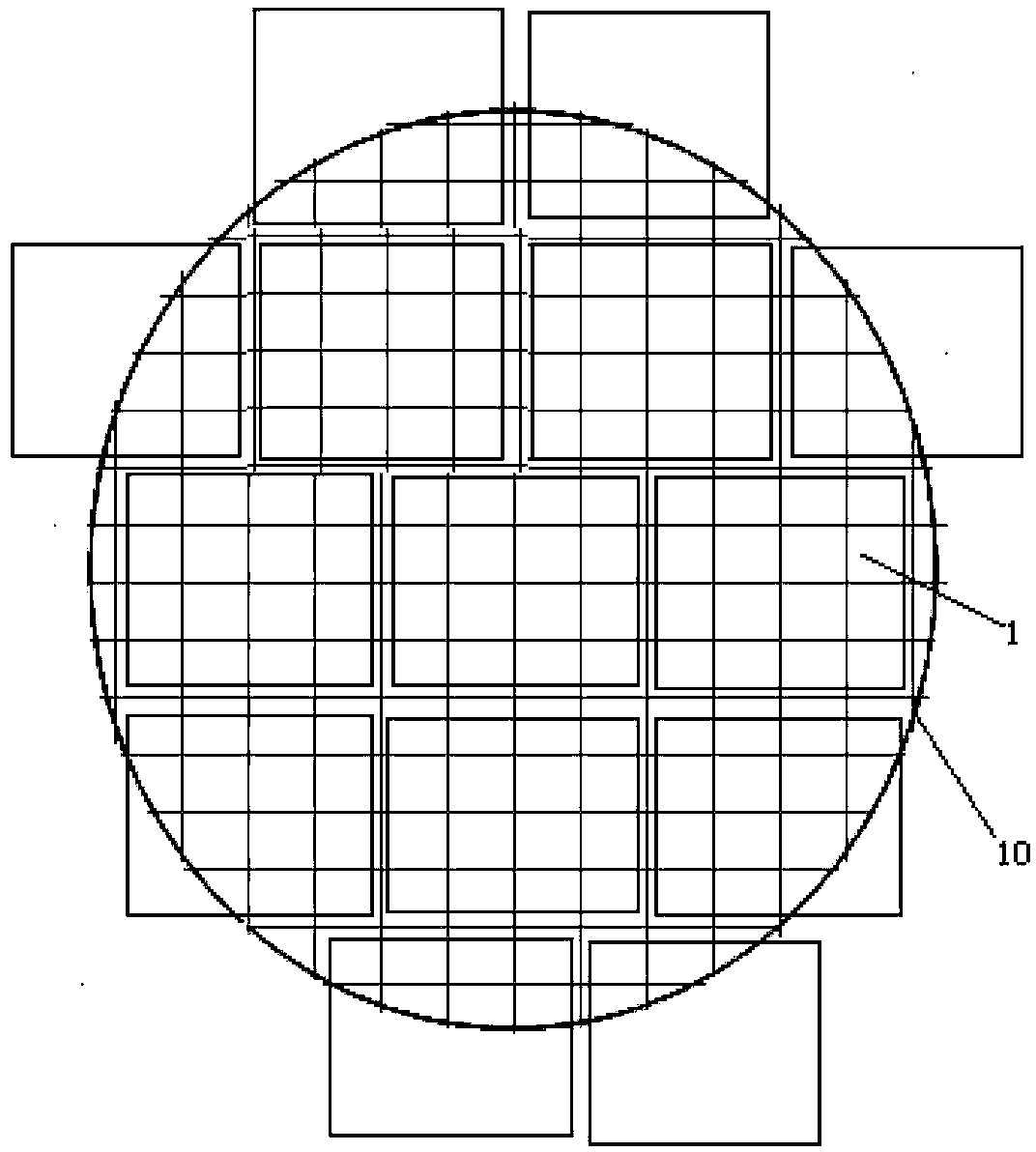

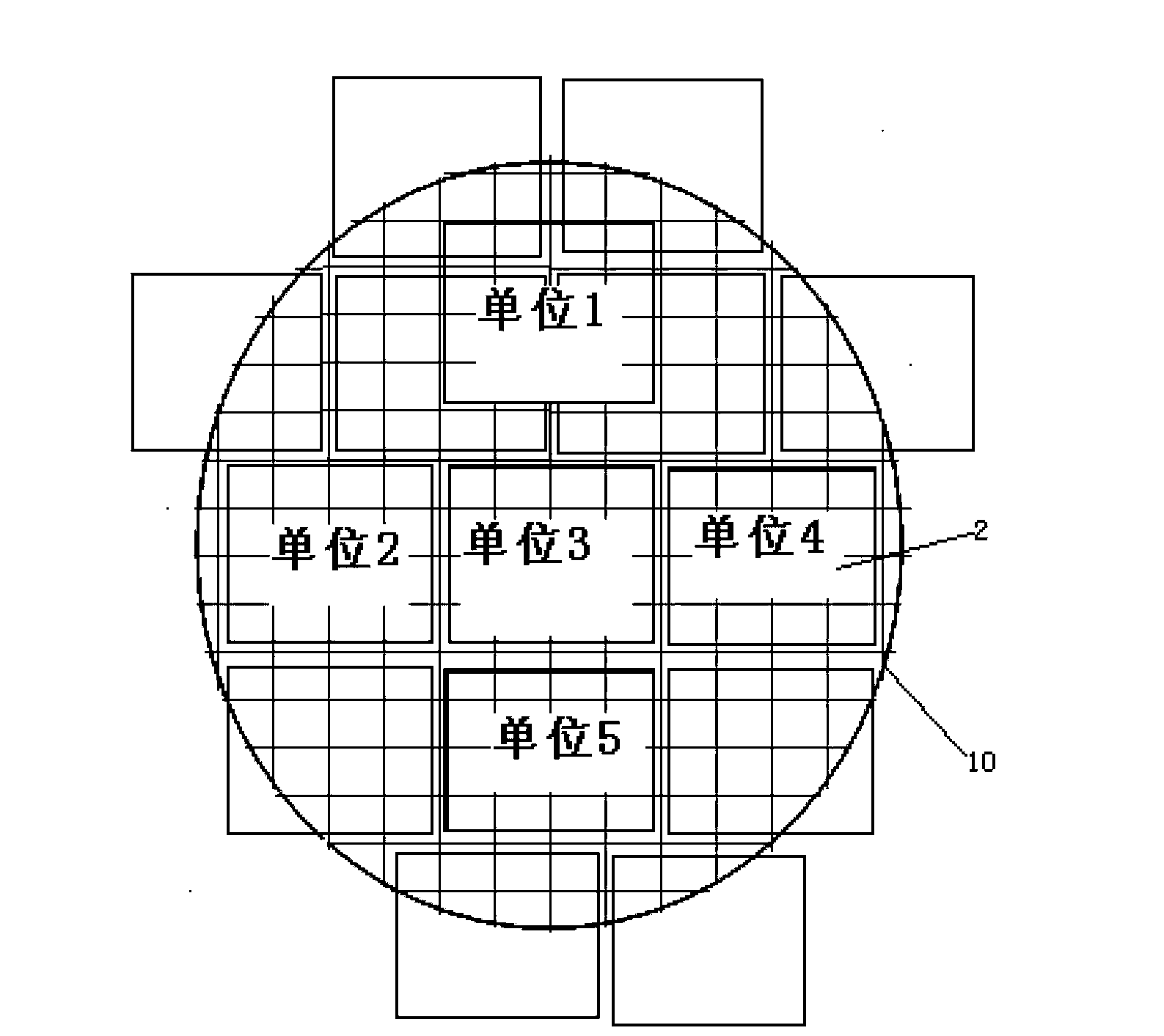

[0030] Such as figure 1 As shown, the trimming method of chip parameters on the wafer of the present invention comprises the following steps:

[0031] In the first step, all the chips on the test wafer 10 are divided into multiple test units ( figure 1 divided into 14 test units1);

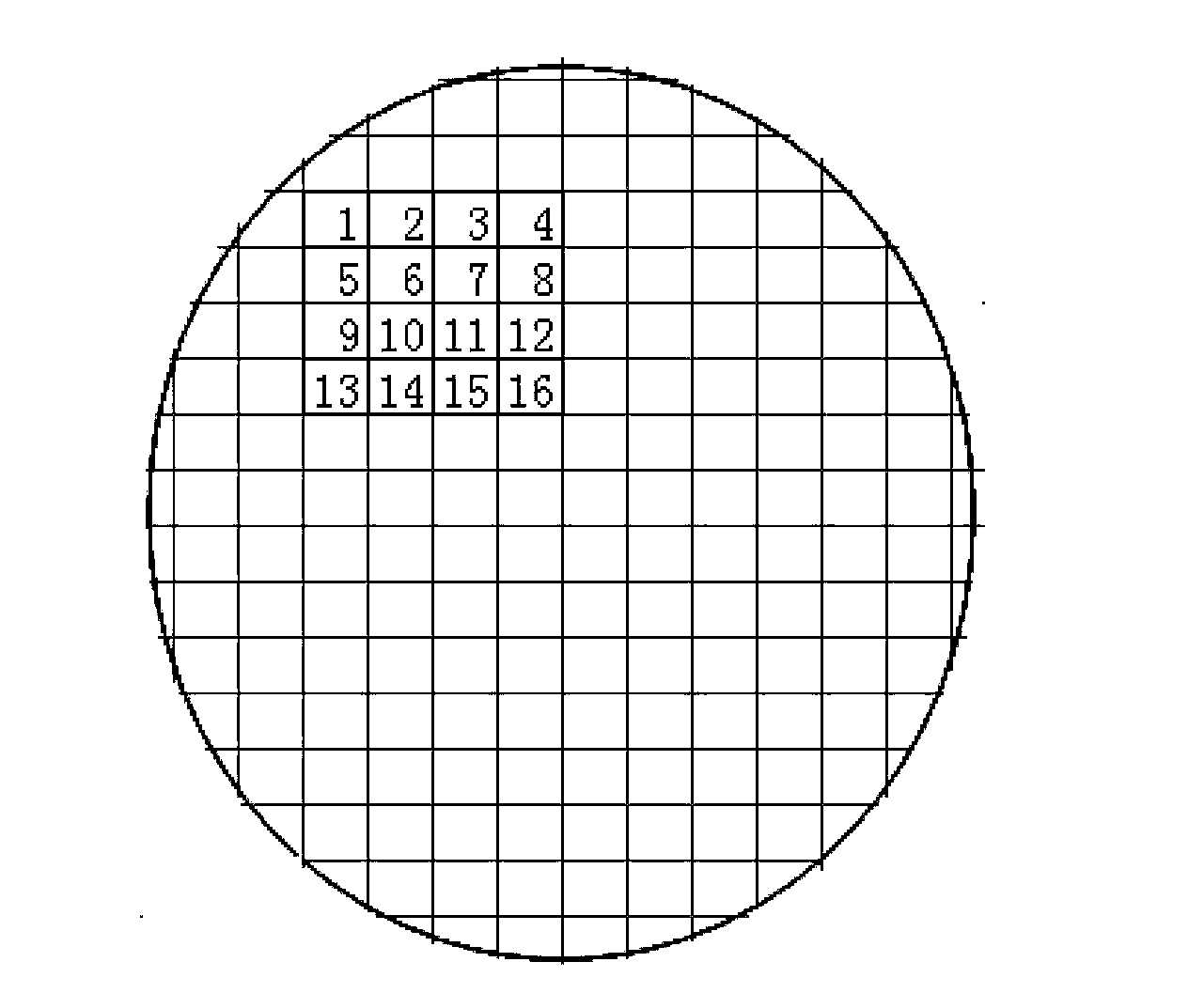

[0032] Such as figure 2 As shown, if the probe card can pierce 16 chips at a time, each test unit contains a maximum of 16 chips, so that the probe card can measure the parameter eigenvalues of all chips in the test unit every time;

[0033] The second step is to measure a parameter that needs to be adjusted by each chip in a test unit through the probe card, and obtain the eigenvalue of the parameter of all chips in the test unit;

[0034] The parameters of the chip can be the reference voltage value of the chip, the functional voltage value of the chip, the current value of the chip, and the frequency of the chip;

[0035] The third step is to take the average value of the parameter eigen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com