A high-speed network strategy matching method based on fpga

A matching method and high-speed network technology, applied in the field of network matching, can solve the problems of large hardware space occupation, complex logic operation, low efficiency, etc., and achieve the effect of low storage space occupation, simple and efficient logic processing, and improved matching efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

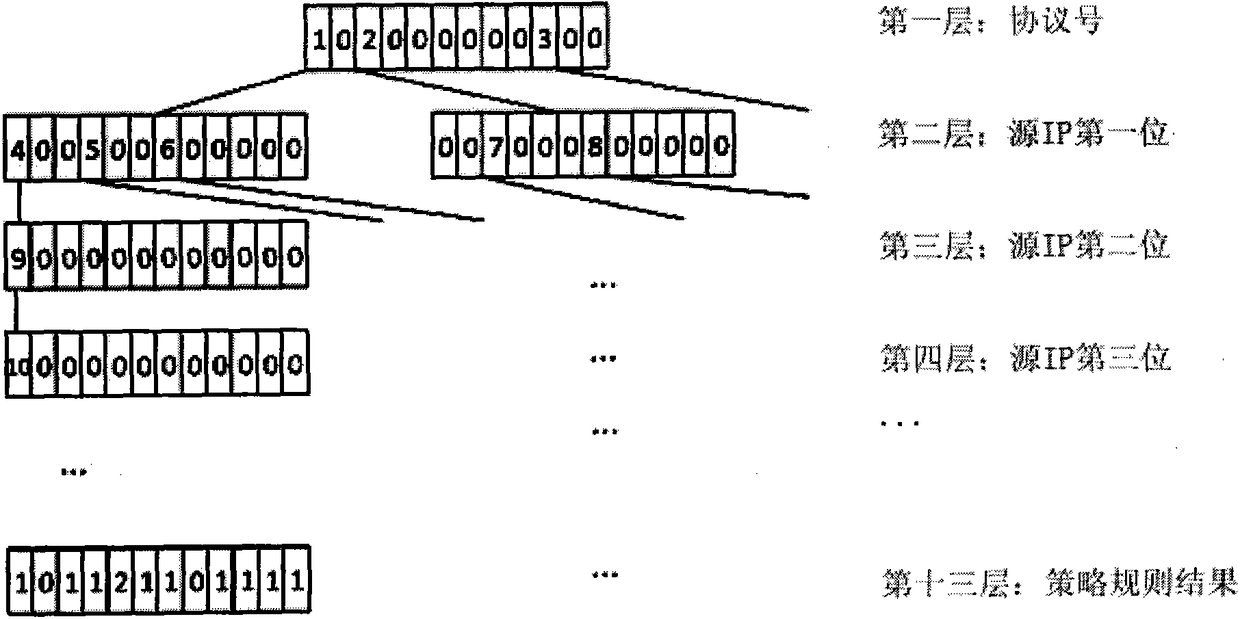

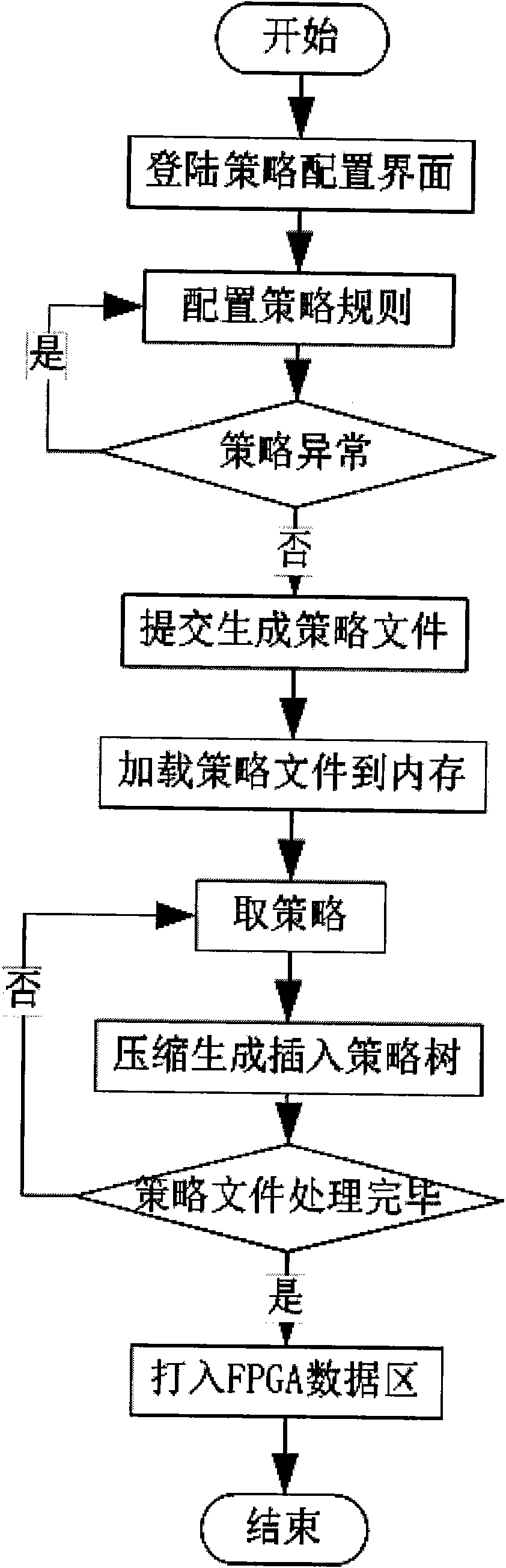

[0034] Such as image 3 , 4 Shown, a kind of FPGA-based high-speed network strategy matching method of the present invention comprises strategy tree generating method and strategy tree matching method;

[0035] The method for generating a strategy tree comprises the steps of:

[0036] Step 1: Set multiple network policy matching conditions on the network policy related interface: quintuple and policy results (such as: clear pass, close pass, discard, fill, etc.);

[0037] Step 2: After the interface is configured, a custom binary mode policy data file is generated in the background of the system;

[0038] Step 3: read the policy data file into memory;

[0039] Step 4: read a policy record from the policy data file;

[0040] Step 5: according to the key information in the policy record, insert FPGA strategy tree by protocol number, source IP, destination IP, source port, destination port and strategy result;

[0041] Step 6: Repeat steps 4 to 5 until all policy records in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com