Method for high-performance fault tolerance of PCIE (Peripheral Component Interface Express) data link layer

A data link layer, high-performance technology, applied in data exchange networks, electrical digital data processing, digital transmission systems, etc. Fault-tolerant performance, realizing error-correcting function, and enhancing the effect of fault-tolerance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

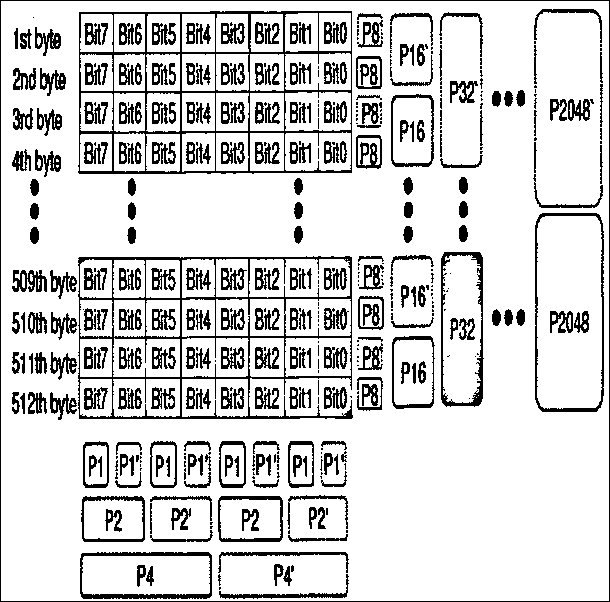

[0021] The present invention is a kind of method for PCIE data link layer high-performance fault-tolerant, described method comprises the following steps:

[0022] 1) Add an ECC encoding circuit at the sending end of the data link layer, and the encoding circuit is responsible for encoding to generate the initial ECC check code of the TLP data packet. An ECC decoding circuit is added to the circuit structure of the receiving end, and the decoding circuit is responsible for generating a new ECC check code, and performing XOR error detection and error correction on the new ECC check code and the initial ECC check code carried by the data. When the decoding circuit detects an error but cannot correct it (beyond the error correction range of the encoding algorithm), an error occurrence identification signal will be generated to indicate that an uncorrectable error has occurred, and the uncorrectable error will be corrected according to the ACK / NAK protocol. The packet is resent. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com