Thin-film transistor substrate and manufacturing method

A technology of thin-film transistors and manufacturing methods, applied in the field of thin-film transistor substrates and their manufacturing, to achieve the effects of compact layout, excellent heat resistance, and increased aperture ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0073] (Structure of liquid crystal display device)

[0074] -TFT Substrate-

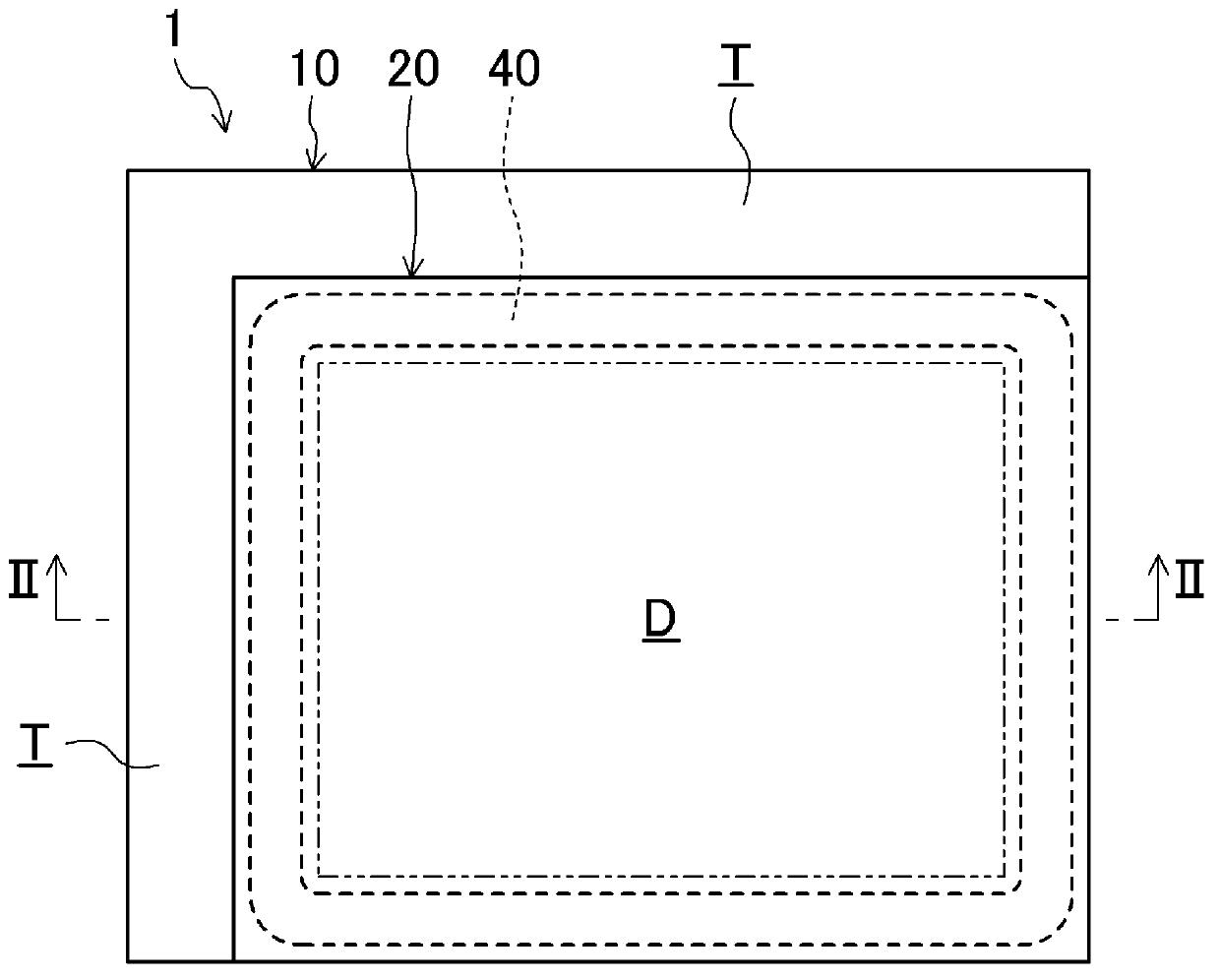

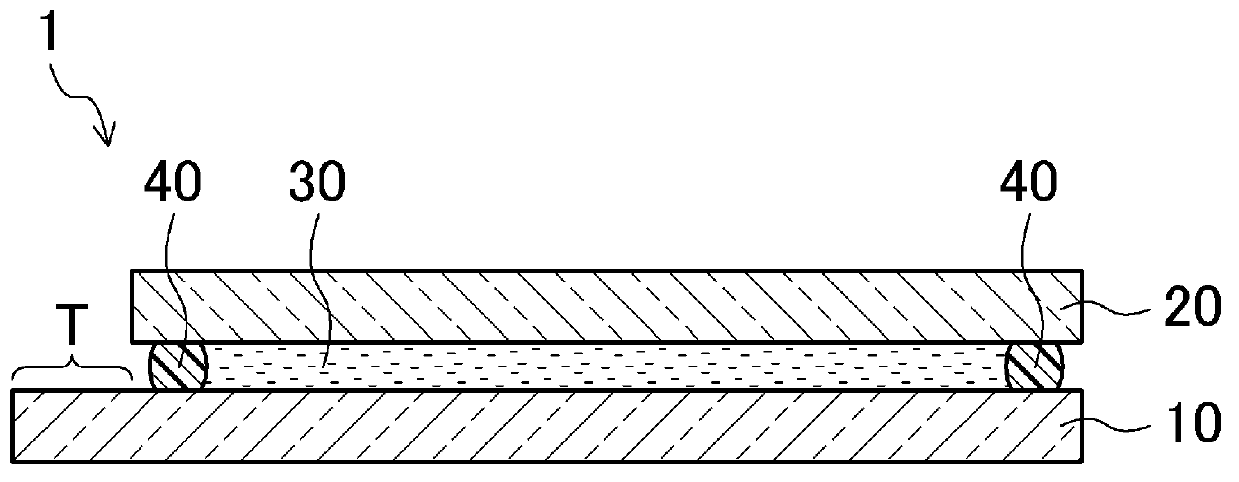

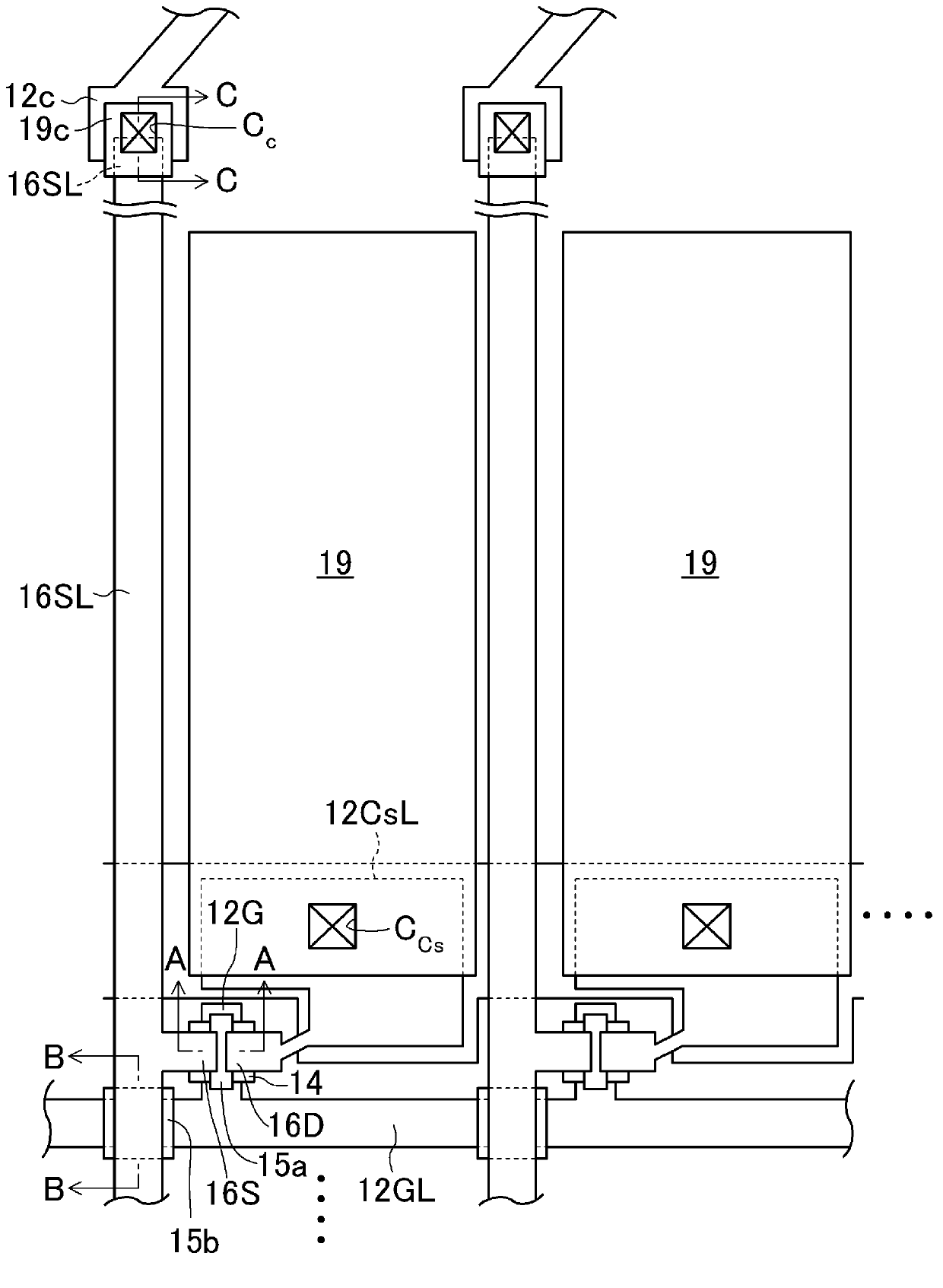

[0075] figure 1 It is a plan view of a liquid crystal display device 1 having a TFT substrate 10 of a thin film transistor according to Embodiment 1, figure 2 yes figure 1 Sectional view of line II-II. in addition, image 3 It is an enlarged plan view of the display area D of the TFT substrate 10 having the TFT of this embodiment, Figure 4 is an enlarged plan view of TFTs in the display region D of the TFT substrate 10, Figure 5 yes Figure 4 Cross-sectional view of the TFT at the V-V line.

[0076] In the liquid crystal display device 1 , a TFT substrate 10 and a counter substrate 20 are disposed so as to face each other, and both are bonded together by a sealing material 40 provided on the outer periphery of the substrates. Furthermore, in a region surrounded by the sealing material 40, a liquid crystal layer 30 is provided as a display medium layer.

[0077] In addition, in the liquid...

Embodiment approach 2

[0125] Next, a liquid crystal display device according to Embodiment 2 will be described.

[0126] -TFT Substrate-

[0127] In the liquid crystal display device 1 , as in Embodiment 1, the TFT substrate 10 and the counter substrate 20 are disposed so as to face each other, and both are adhered by the sealing material 40 provided on the outer peripheral edge of the substrates. In addition, a liquid crystal layer 30 is provided as a display medium layer in a region surrounded by the sealing material 40 .

[0128] In addition, in the liquid crystal display device 1 , a display region D for image display is formed in a portion inside the sealing material 40 , and a terminal region T is formed in a portion protruding from the counter substrate 20 of the TFT substrate 10 .

[0129] TFT substrate 10, such as Figure 10 As shown, in the display area D, there are: a plurality of gate signal lines 12GL arranged to extend in parallel to each other; source signal lines 16SL; and a plur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com