Decoupling capacitor and integrated circuit provided with same

A technology of decoupling capacitors and decoupling capacitors, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as large ESD risks, reduced protection capabilities, gate oxide breakdown, etc., and achieve the effect of enhancing ESD protection characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

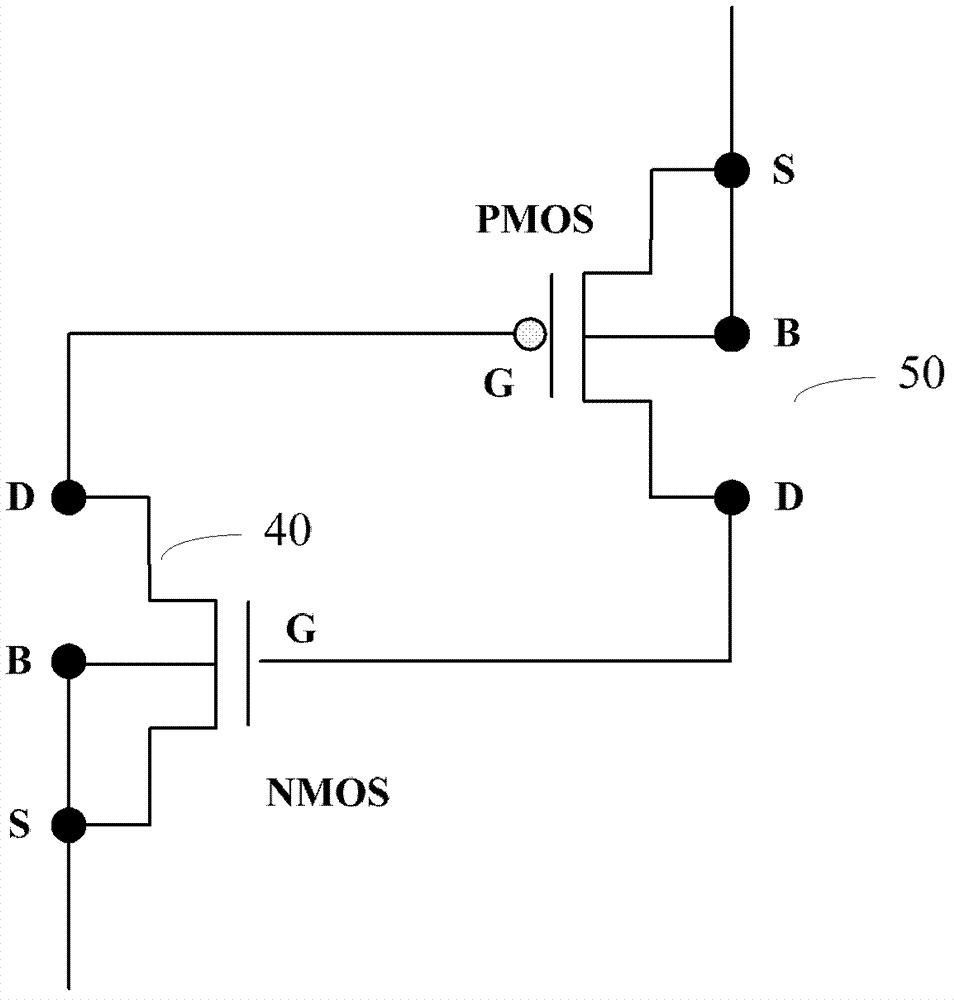

[0034] refer to image 3 , shows a second embodiment of a decoupling capacitor of the present application, including an NMOS transistor 40 and a PMOS transistor 50 . Wherein, the drain (D) of the PMOS transistor 50 is connected to the gate (G) of the NMOS transistor 40 , and the drain (D) of the NMOS transistor 40 is connected to the gate (G) of the PMOS transistor 50 . Wherein, the source (S) voltage of the PMOS transistor is higher than the source (S) voltage of the NMOS transistor. In this application, the gate of the NMOS transistor is connected to the VDD power supply line through the channel resistance of the PMOS transistor (that is, the source of the PMOS transistor is connected to the power supply), and the gate of the PMOS transistor is connected to GND through the channel resistance of the NMOS transistor ( That is, the source of the NMOS transistor is grounded). It is this increased channel resistance that enhances the ESD protection characteristics. It can be u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com