Software and hardware synergic simulation verification platform and construction method thereof

A software-hardware collaboration and verification platform technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as imperfect functional equivalence verification platforms, inapplicable equivalence verification, and unsatisfactory time , to achieve the effect of convenient design work, speed up and save trouble

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

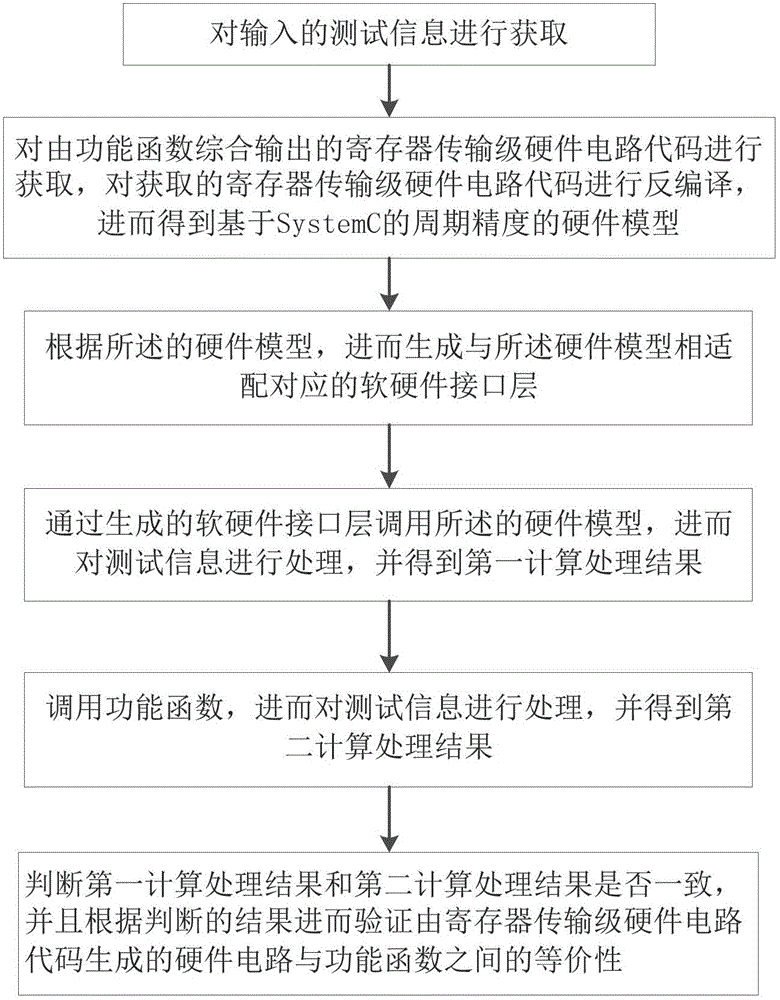

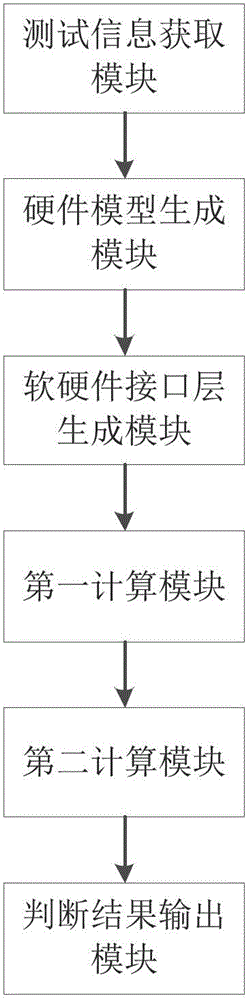

[0037] Depend on figure 1 As shown, a method for building a verification platform for software-hardware co-simulation, the method includes:

[0038] Obtain the input test information;

[0039] Obtain the register-transfer-level hardware circuit code synthesized by the functional function, and decompile the obtained register-transfer-level hardware circuit code, and then obtain a hardware model based on SystemC cycle accuracy;

[0040] According to the hardware model, a software-hardware interface layer corresponding to the hardware model is generated;

[0041] Invoking the hardware model through the generated software and hardware interface layer, and then processing the test information, and obtaining a first calculation and processing result;

[0042] call the function, and then process the test information, and obtain the second calculation and processing result;

[0043] Judging whether the first calculation processing result is consistent with the second calculation pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com