Method for eliminating internal nodes of metal-oxide-semiconductor field effect transistor (MOSFET) used in rapid circuit simulation

A technology of internal nodes and nodes, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of losing necessity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

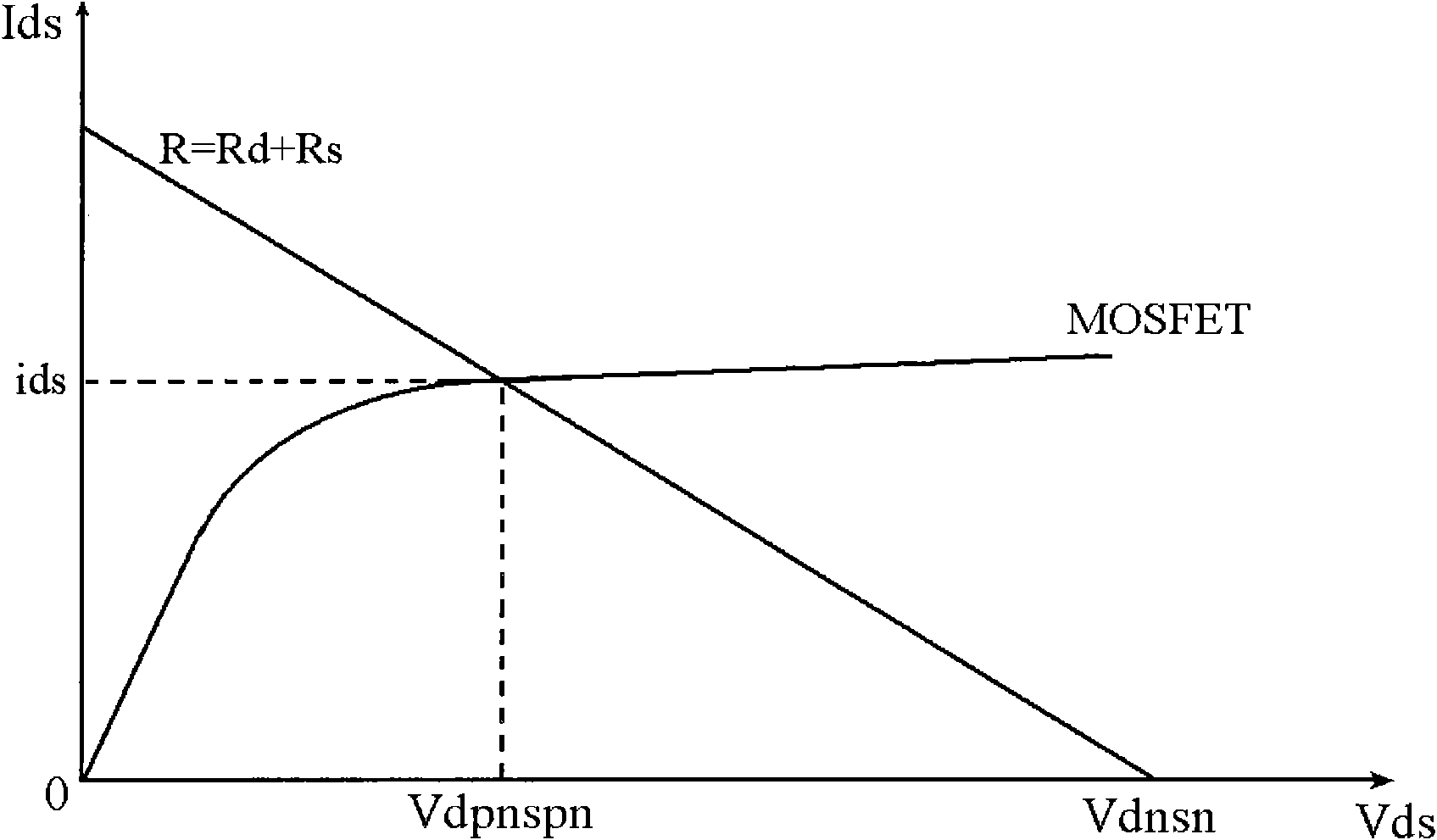

[0056] MOSFET is a 4-terminal device such as figure 1 As shown, its external nodes are Dn, Gn, Sn and Bn respectively. When the parasitic resistance R of the Dn terminal and the Sn terminal d and R s When it cannot be ignored, we will use a 6-node circuit network to equivalent MOSFET, and these 6 nodes are Dn, Dpn, Sn, Spn, Gn and Bn respectively. Also included in this circuit network are Ids (the intrinsic part of MOSFET), two current sources of Isub and two diodes of Dbs and Dbd.

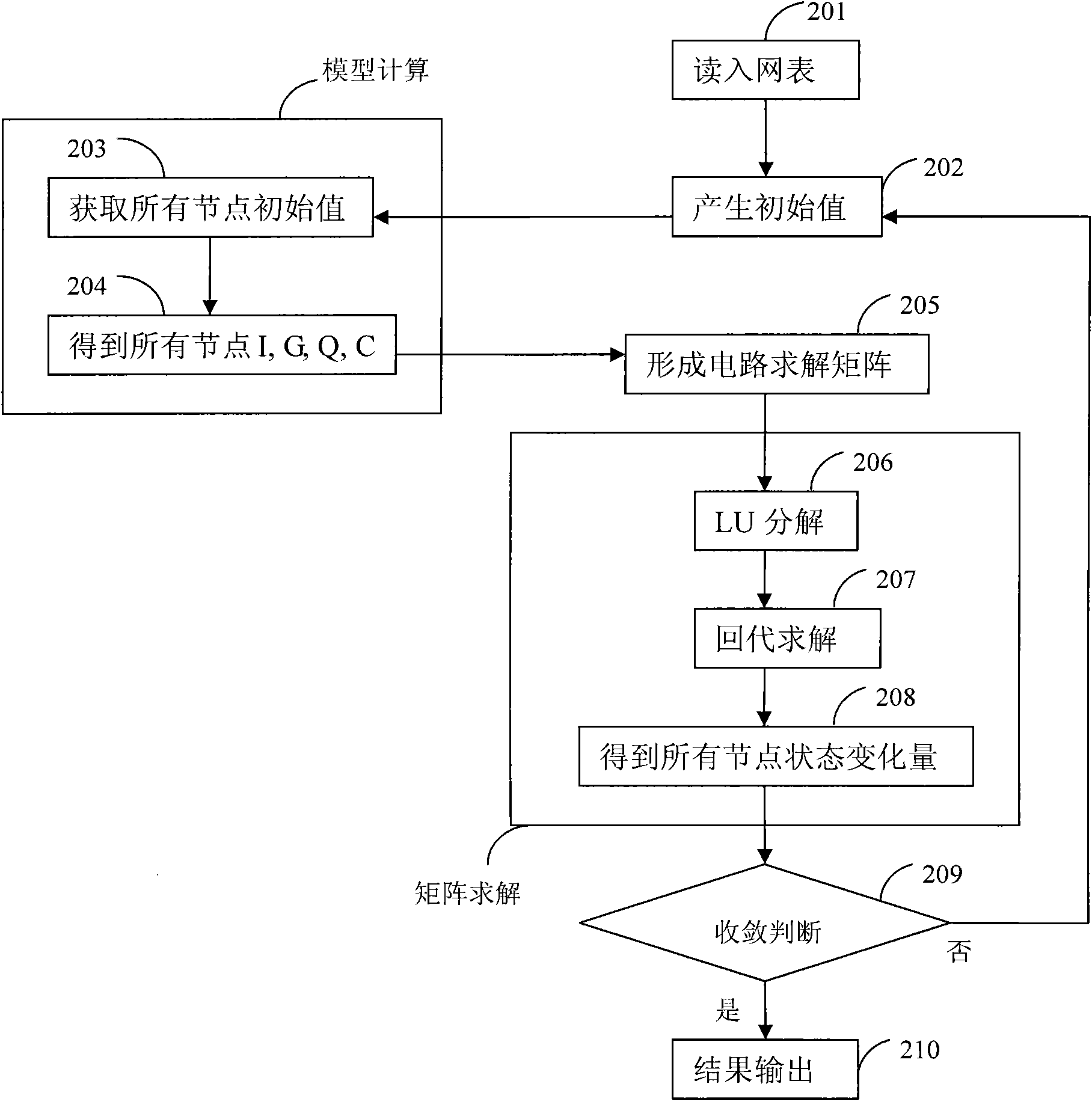

[0057] If a circuit contains such figure 1 6-node MOSFET shown, then the conventional circuit simulation flow is as follows figure 2 shown. The circuit simulator first reads in the netlist (201), and then generates a set of voltages and branch currents of all nodes (including internal nodes of MOSFETs) of each device for model calculation, which is the initial value of the circuit (202). Give this group of circuit state initial values to the model Engine (203), enter the model calculation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com