Programmable logic array intellectual property (IP) core and system integration method thereof

A programming logic and array technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems affecting data transmission efficiency, SOC system level design impact, increasing data channel delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

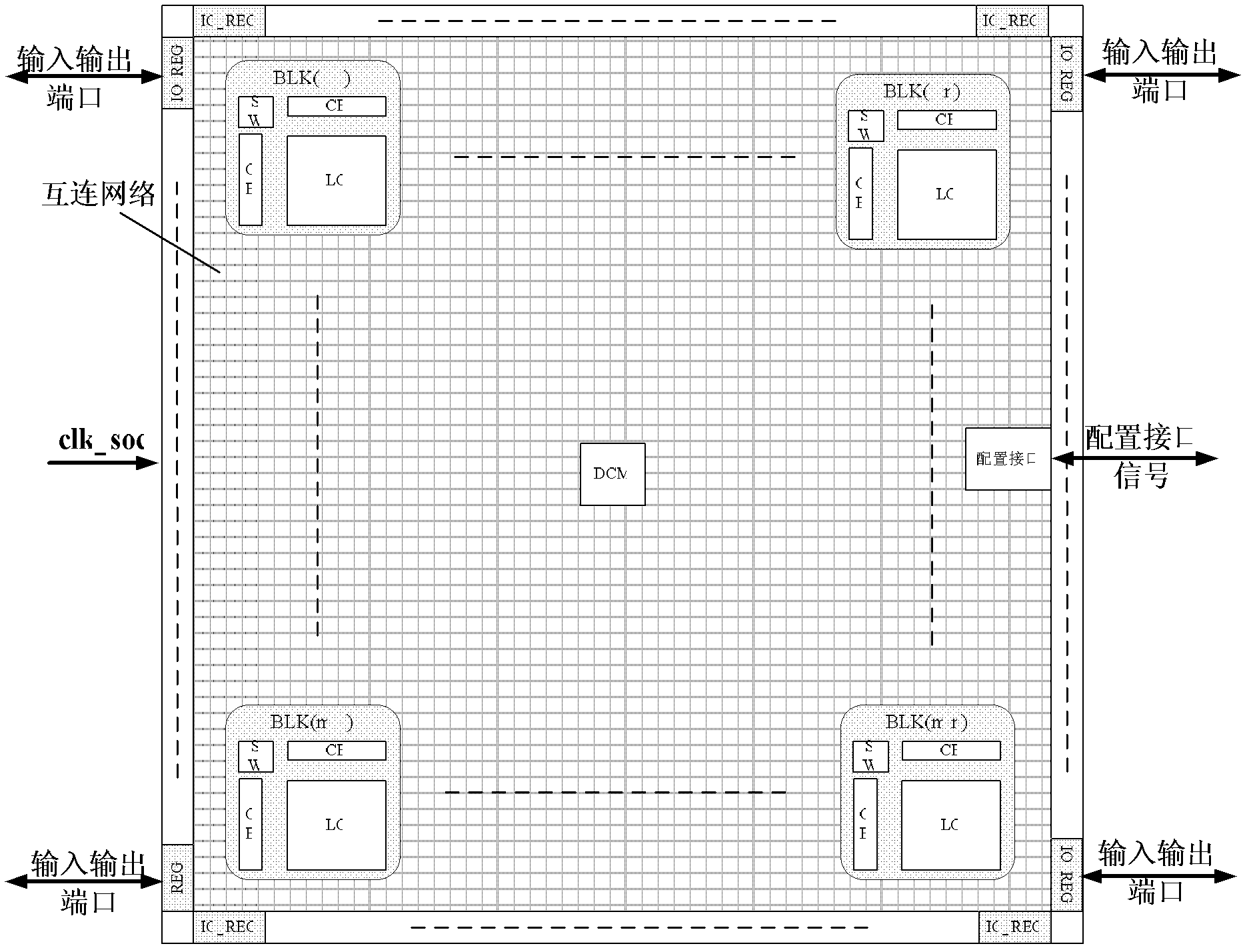

[0019] The proposed programmable logic array IP core of the present invention is realized based on static memory (SRAM), and its circuit structure is as follows figure 1 As shown, the programmable logic array IP core is mainly composed of multiple programmable logic array blocks BLK, interconnection network, clock management module DCM, input and output ports, and configuration interfaces and other modules.

[0020] Among them, the IP core contains programmable logic array blocks BLK with the number of m rows×n columns (m, n≥2), and each BLK has similar structural characteristics. The logical scale of the IP core is mainly determined by the number of BLKs, which can be By increasing or decreasing the BLK, the logical scal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com