On-chip interconnection structure and method of multi-core network processor

A network processor and interconnection structure technology, applied in the field of on-chip interconnection structure, can solve the problems of large area cost and complex structure, and achieve the ideal effect of high communication bandwidth, simple on-chip interconnection structure, area and cost control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The structure of the present invention will be further described below in conjunction with the accompanying drawings.

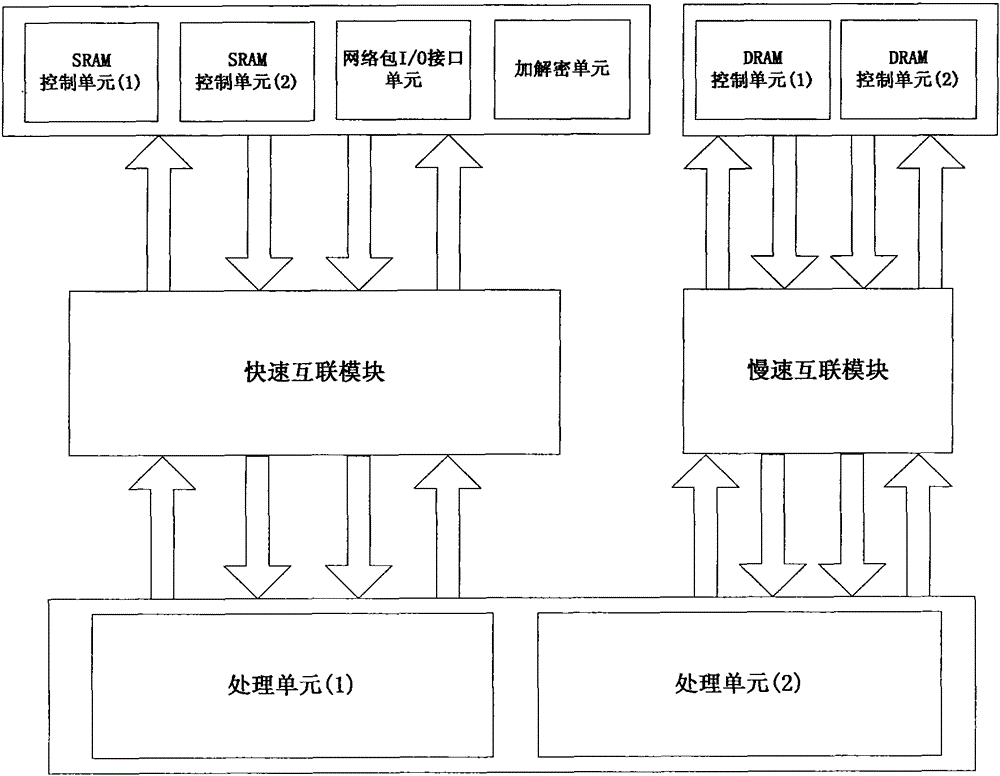

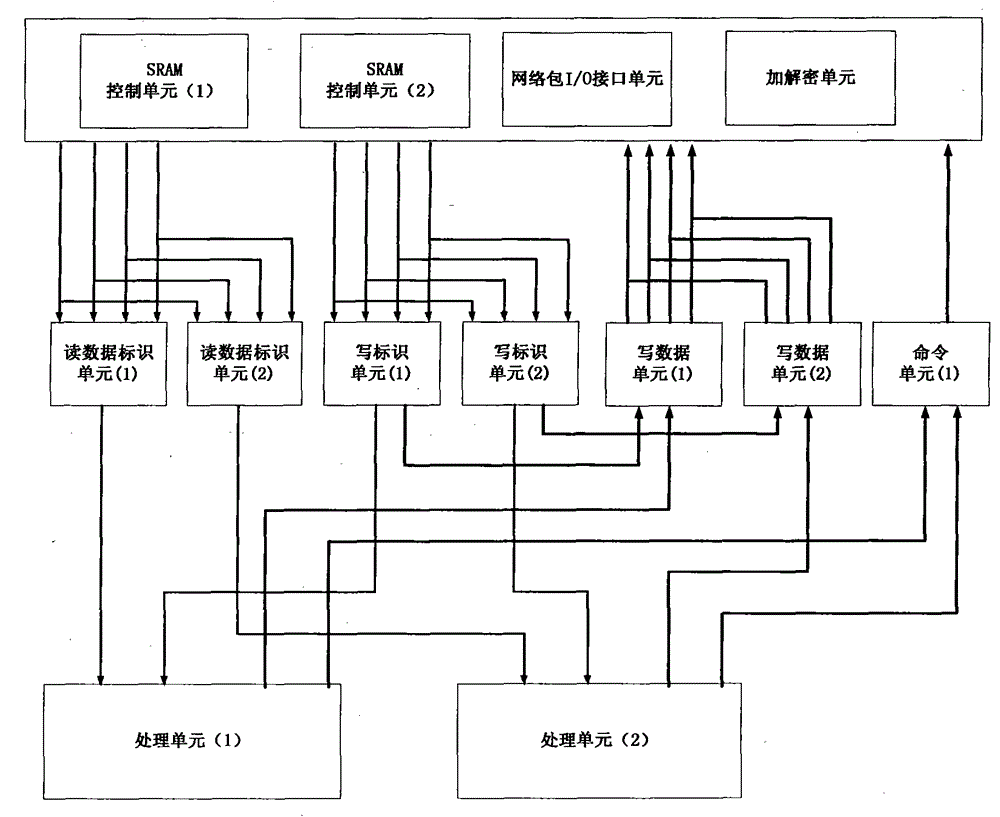

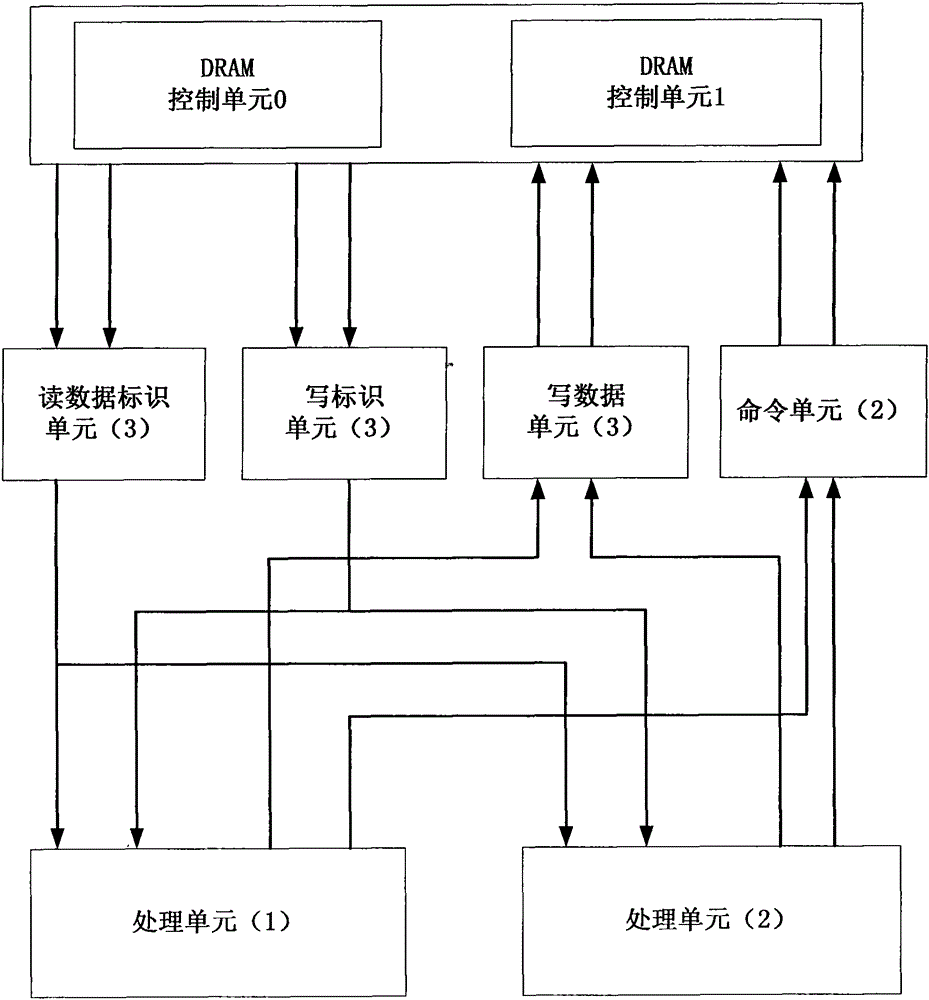

[0056] Refer to attached figure 1 , the structure of the present invention comprises processing unit (1), processing unit (2), SRAM control unit (1), SRAM control unit (2), network packet I / O interface unit, encryption and decryption unit, DRAM control unit (1) , DRAM control unit (2). Because the SRAM control unit (1), the SRAM control unit (2), the network packet I / O interface unit, the encryption and decryption unit and the DRAM control unit (1), and the DRAM control unit (2) are in the speed of receiving data and sending data There are differences, so the on-chip interconnect is divided into fast interconnect modules and slow interconnect modules. At the same time, in order to make the on-chip interconnect structure have good scalability, processing unit (1), processing unit (2), SRAM control unit (1), SRAM control unit (2), network packet I / O in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com