Anti-false-triggering power supply clamp ESD (Electro-Static Discharge) protection circuit

一种ESD保护、电源的技术,应用在紧急保护电路装置、用于限制过电流/过电压的紧急保护电路装置、电路装置等方向,能够解决无源电容C2和C3大、电阻难达到很大阻值、芯片版图面积增加等问题,达到版图面积减小、漏电小、提高开启时间的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

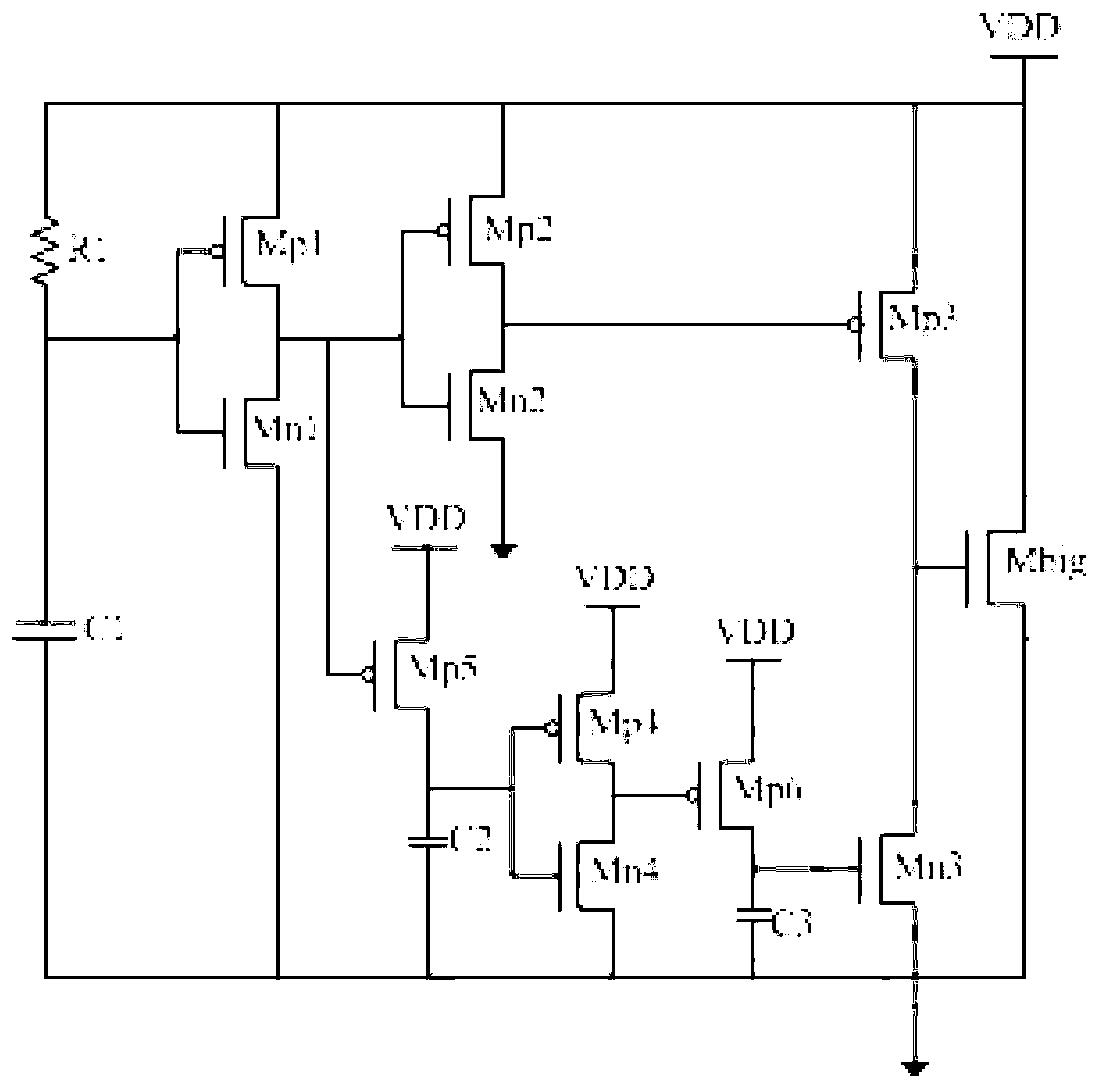

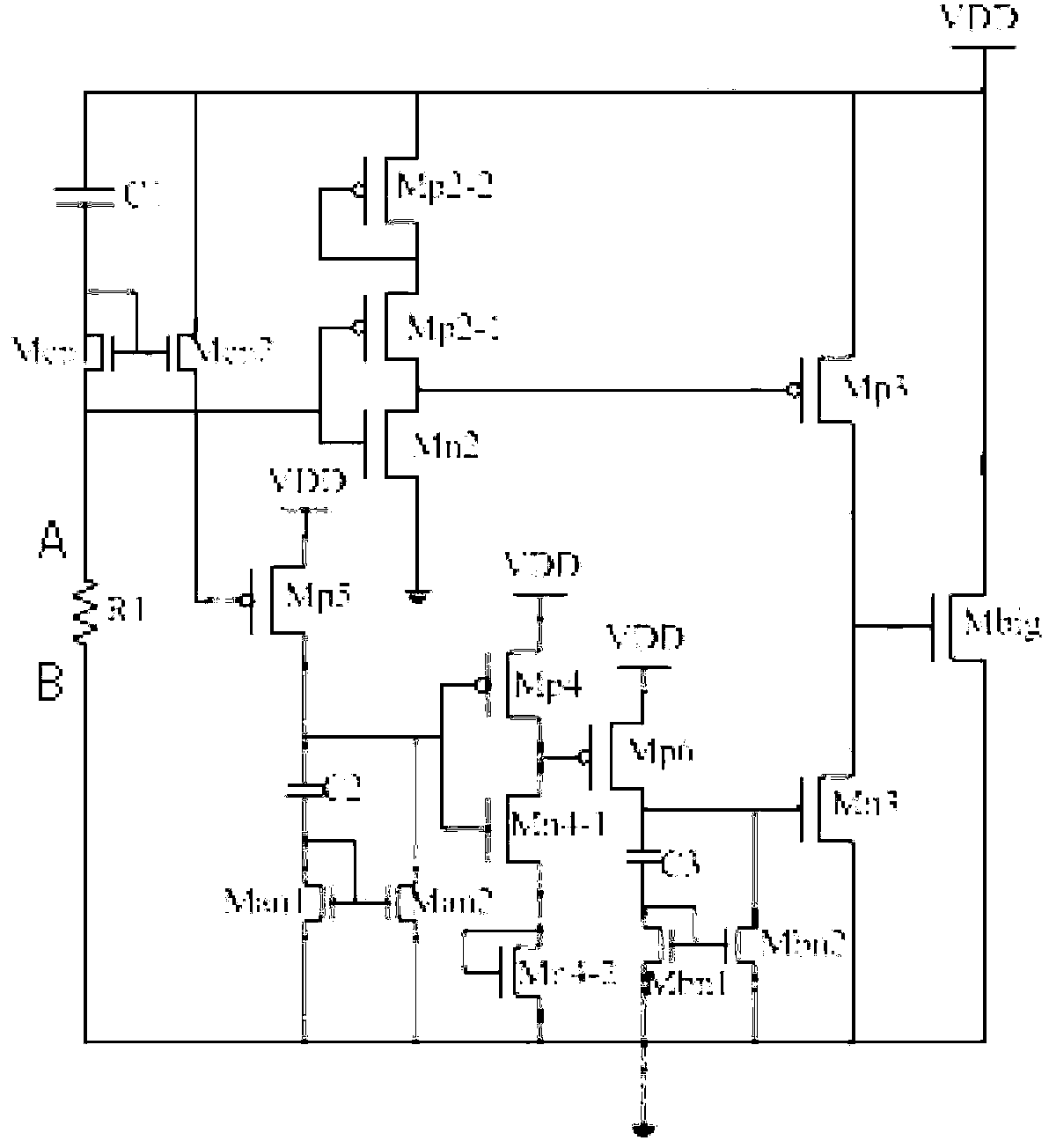

[0024] figure 2 It is a structural schematic diagram of an anti-false trigger type power supply clamp ESD protection circuit according to an embodiment of the present invention. The circuit includes: an ESD impact detection component, a discharge transistor, an opening path of the discharge transistor, and an off path of the discharge transistor.

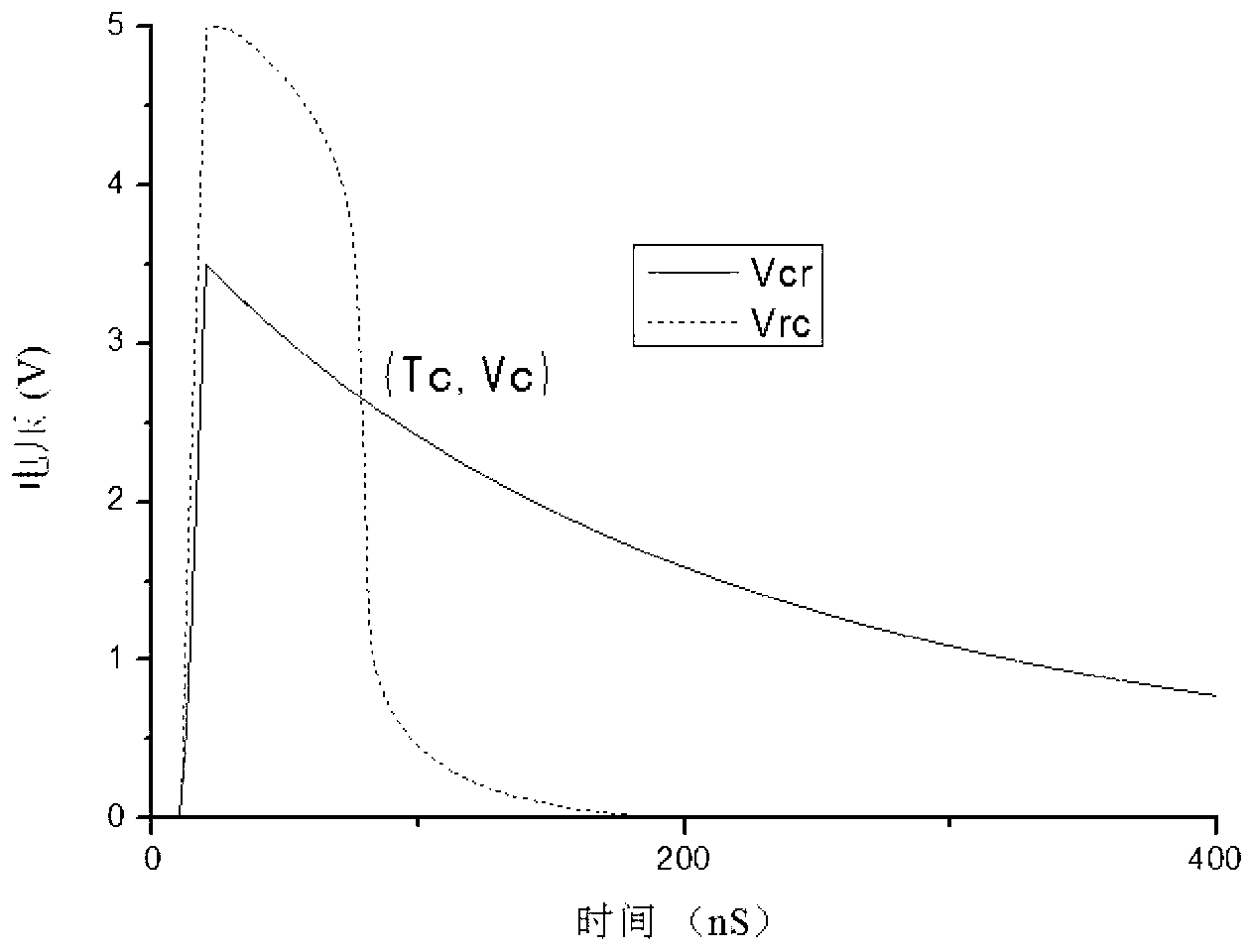

[0025]The ESD impact detection part is used to identify whether the impact added between the power line and the ground wire is an ESD impact, if it is an ESD impact, a corresponding signal is sent to open the discharge transistor, and if it is powered on normally, the discharge transistor is not opened Transistor; the discharge transistor is used to provide a low-resistance discharge path for the electrostatic charge brought by the impact when the ESD impact comes; the discharge transistor opens the path f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com