Preparation method of back passivated battery

A technology of back passivation and batteries, which is applied in the manufacture of circuits, electrical components, final products, etc., can solve the problems of complex technology and high energy consumption, and achieve the effects of good spectral response, improved utilization rate, and good electrical passivation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

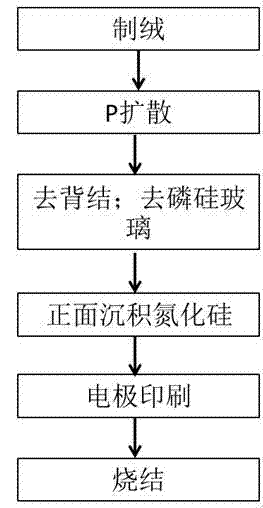

Problems solved by technology

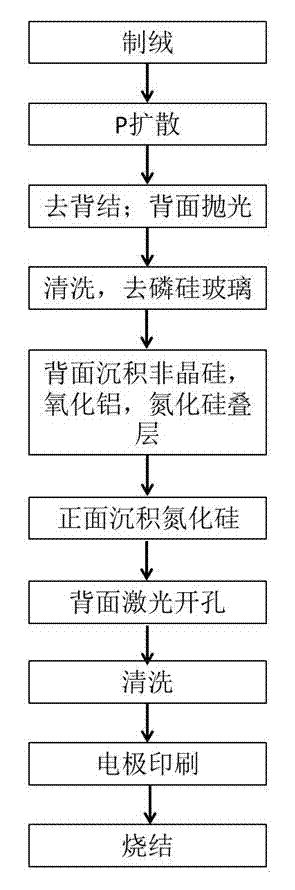

Method used

Image

Examples

Embodiment 1

[0025] The operation steps are as follows:

[0026] Select a P-type monocrystalline silicon wafer with a crystal plane of (100) and a doping concentration of 2 Ω·cm, perform routine cleaning, and prepare a surface texture in a 1.5% KOH solution at a temperature of 70°C for 20 minutes.

[0027] Put the textured silicon wafer into the P diffusion tube for diffusion, the diffusion temperature is 830°C, and the diffusion square resistance is 60Ω / cm.

[0028] Etch and polish the backside of the silicon wafer in 20% KOH solution at a temperature of 70°C for 5 minutes.

[0029] with the main component being H 2 o 2 and NH 3 .H 2 The mixed solution of O was used to clean the back of the silicon wafer for 15 minutes, and the front and back of the silicon wafer were cleaned with 5% HF solution for 5 minutes.

[0030] A laminated passivation film of amorphous silicon, aluminum oxide and silicon nitride is deposited on the back of the silicon wafer by PECVD with a thickness of 83nm. ...

Embodiment 2

[0037] The operation steps are as follows:

[0038] Select a P-type monocrystalline silicon wafer with a crystal plane of (100) and a doping concentration of 1 Ω·cm, perform routine cleaning, and prepare a suede surface in a 1% KOH solution at a temperature of 70°C for 24 minutes.

[0039] Put the textured silicon wafer into the P diffusion tube for diffusion, the diffusion temperature is 880°C, and the diffusion square resistance is 65Ω / cm.

[0040] Etch and polish the backside of the silicon wafer in 15% KOH solution at a temperature of 74°C for 5 minutes.

[0041] with the main component being H 2 o 2 and NH 3 .H 2 Clean the back of the silicon wafer with a mixed solution of O for 20 minutes, and clean the front and back of the silicon wafer with 10% HF solution for 3 minutes.

[0042] Deposit amorphous silicon, aluminum oxide and silicon nitride lamination passivation film with a thickness of 75nm on the back of the silicon wafer by PECVD.

[0043] A silicon nitride ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com