Dynamic comparator with large offset voltage correction range

A dynamic comparator, offset voltage technique used in improving amplifiers to reduce temperature/supply voltage variations, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Referring to the accompanying drawings, the embodiments of the dynamic comparator with a large offset voltage correction range will be described in detail below. It should be emphasized that the following description is only exemplary and not intended to limit the scope of the invention and its application.

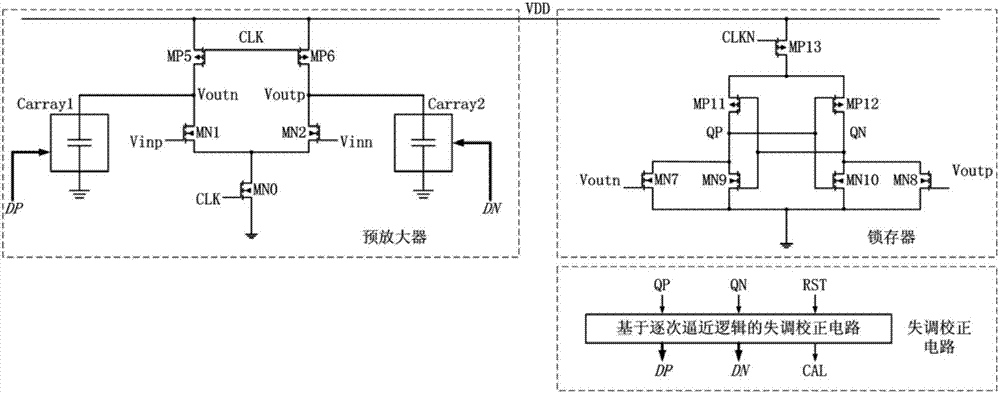

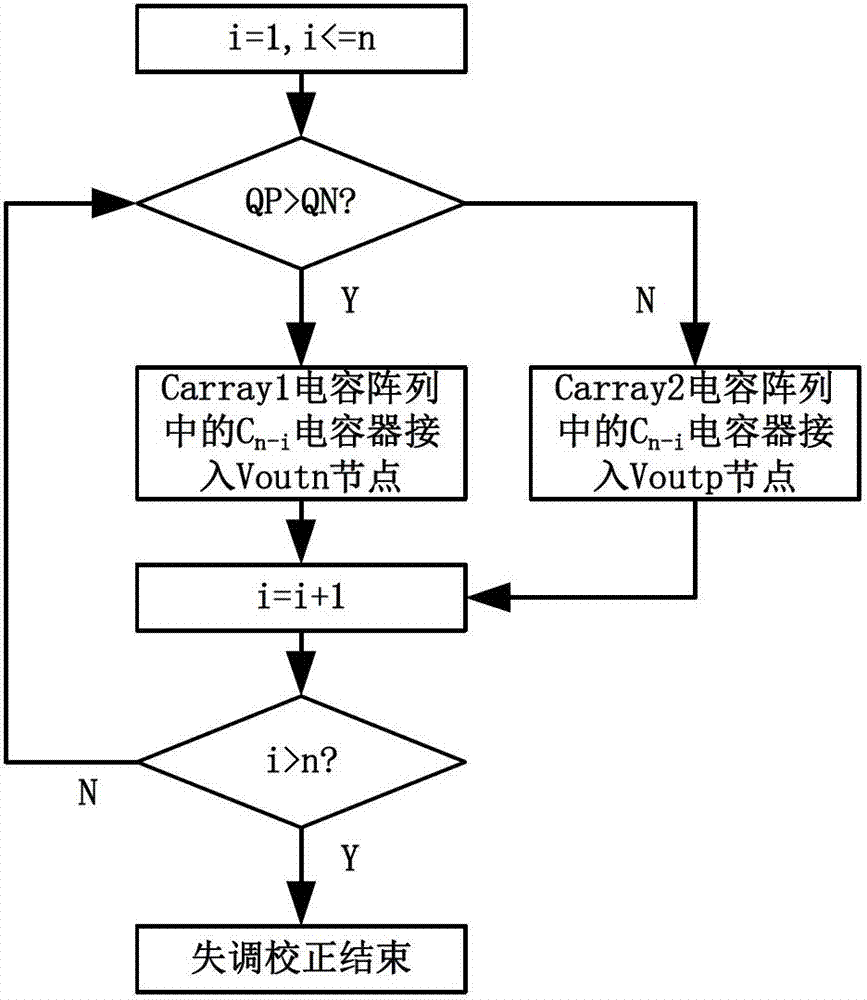

[0027] Figure 4 It is the schematic diagram of the dynamic comparator proposed by the present invention. The dynamic comparator consists of a pre-amplifier, a latch and an offset correction circuit based on successive approximation logic.

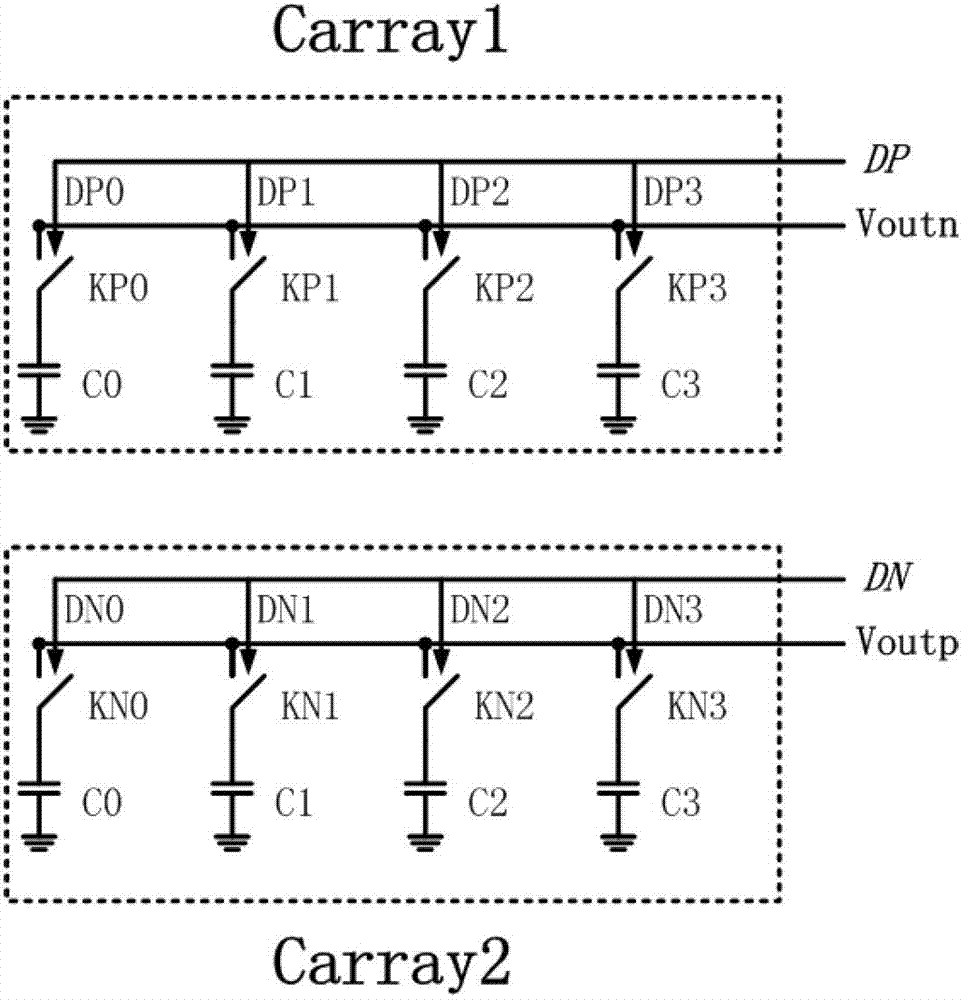

[0028]In the pre-amplifier, the NMOS transistor MN0 is a bias current source, and its gate is connected to an externally provided clock signal CLK. The MN1 and MN2 tubes are differential input pair tubes and are also NMOS tubes. Their gates receive the compared signals respectively. When the comparator is corrected, the two input ports are short-circuited. The PMOS transistors MP5 and MP6 are load MOS transistors, and their ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com