Program updating method for FPGA (Field Programmable Gate Array)/DSP (Digital Signal Processor) embedded system

An embedded system and program update technology, which is applied in the direction of program control device, program loading/starting, etc., can solve the problems of large size, occupying more address lines and data lines, and the JTAG interface is invisible to users, etc., and achieves small size , reduced complexity, and fewer pin counts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

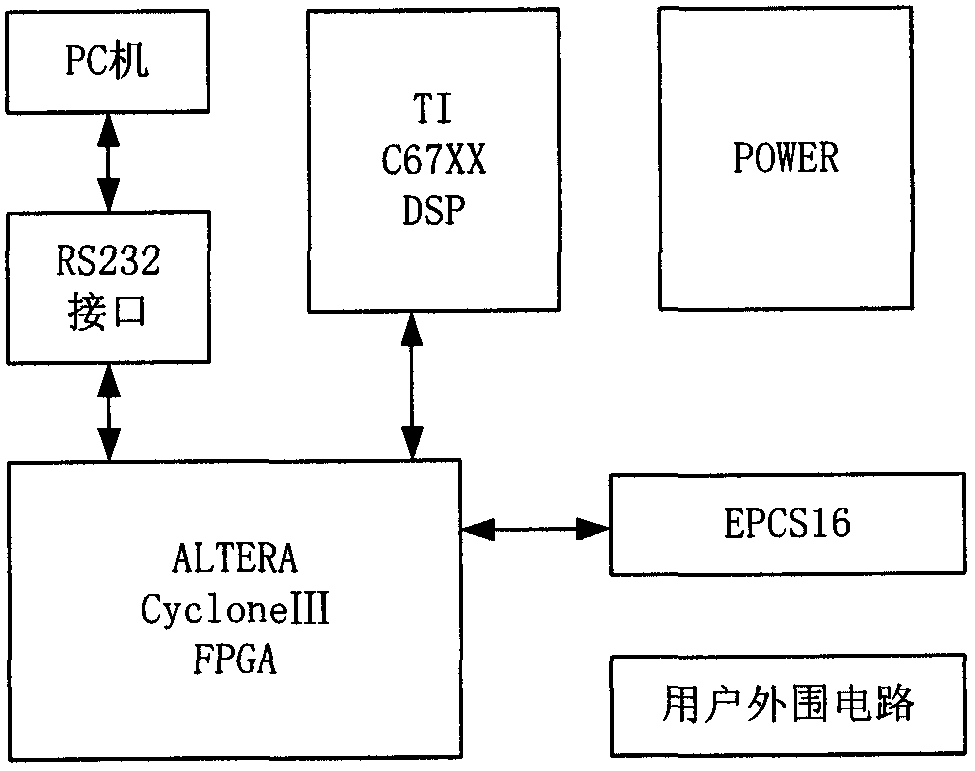

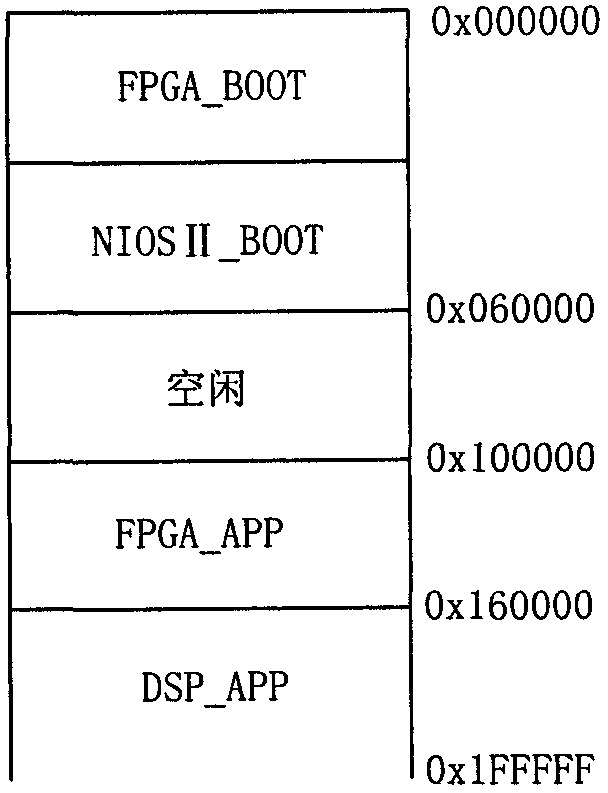

[0026] figure 1 It is the hardware structure of the embedded system of the present invention. The system includes an FPGA chip, a DSP chip and an EPCS chip. The present invention selects cycloneIII series FPGA chips of ALTERA Company, and this series FPGA supports remote configuration technology. Choose TI's C67XX series DSP chips. FPGA special configuration chip chooses EPCS16, which is used to store FPGA hardware configuration data and DSP application program data, which has a storage space of 16Mbit. FPGA is plugged with a communication interface chip, which can be used as a user communication interface, and also used to communicate with the host computer to update the program.

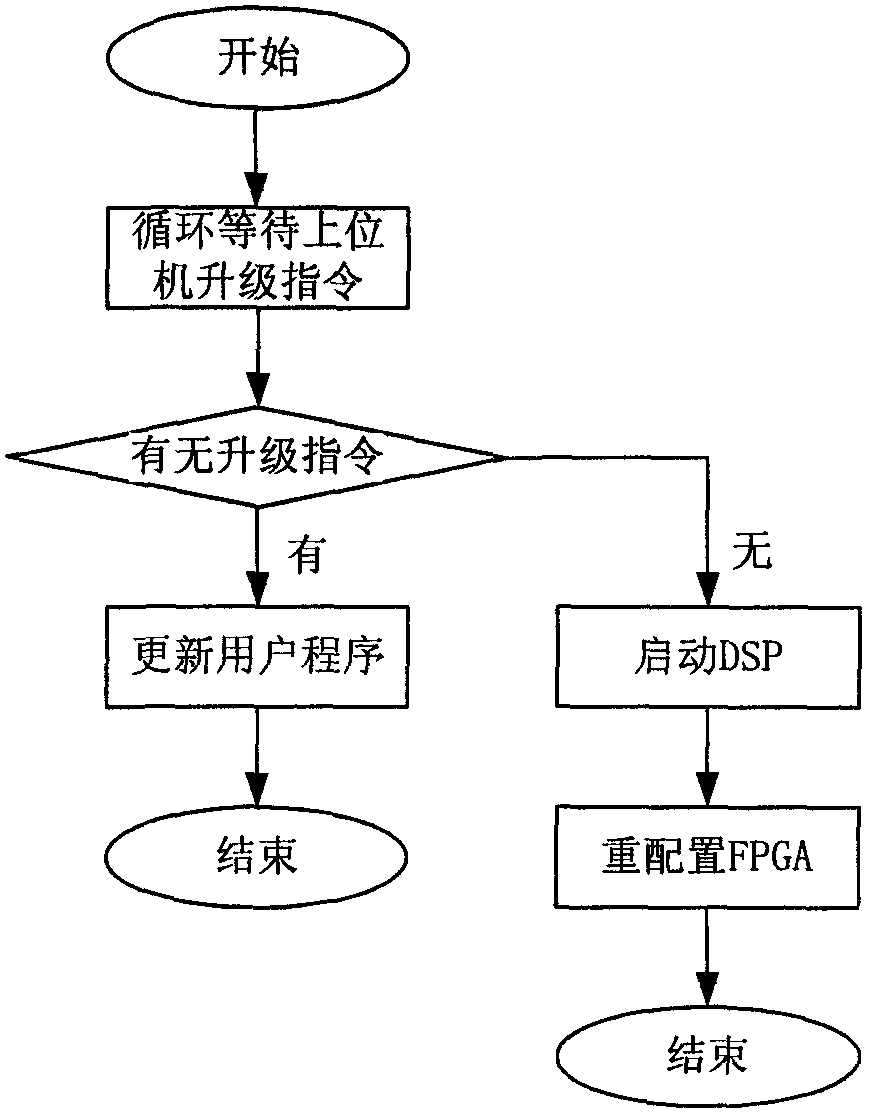

[0027] Such as Figure 5 As shown, the invention provides a kind of program updating method of FPGA / DSP embedded system, and the steps are as follows: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com