Floating-point accumulation/gradual decrease operational method with floating-point precision maintaining function

A floating-point precision and floating-point technology, which is applied in computing, instruments, and electrical digital data processing, can solve problems such as truncation errors, truncation and rounding errors, and achieve the goals of reducing reading, increasing effective digits, and improving performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

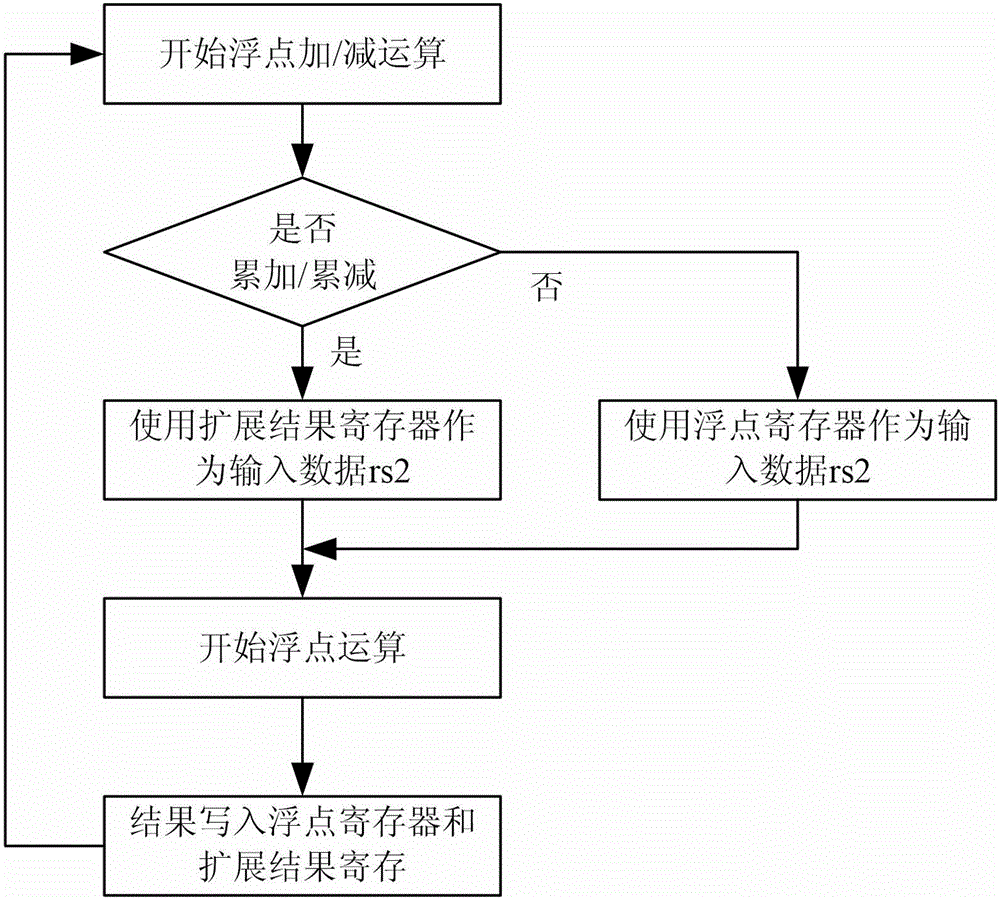

[0023] like image 3 As shown, the implementation steps of the floating-point accumulation / accumulation and subtraction operation method with the function of maintaining floating-point precision in this embodiment are as follows:

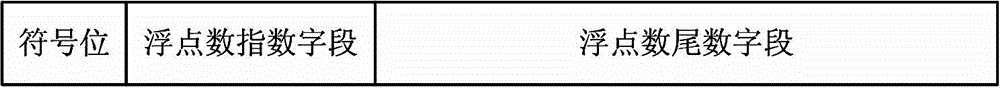

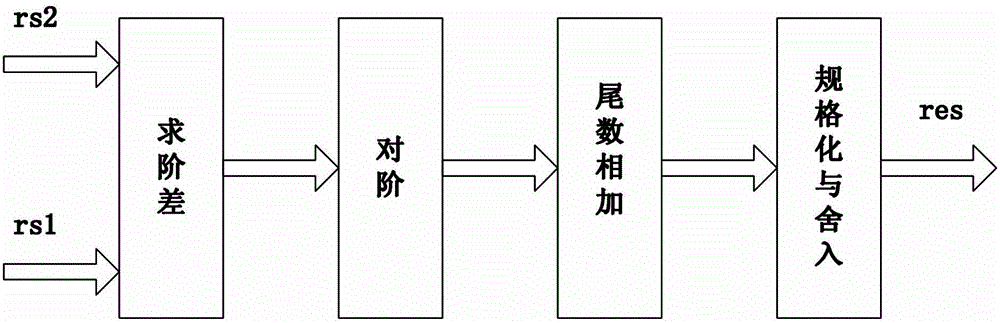

[0024] 1) Pre-expand the width of the order register so that the floating-point operation before the floating-point operation does not perform data truncation, expand the width of the result register to store temporary operation results, and expand the width of the binary adder to meet the expanded width. The order register and the extended result register; when performing operations, the floating-point accumulation / subtraction operation is decomposed into the first floating-point addition / subtraction instruction and the subsequent floating-point accumulation / subtraction instruction to obtain the first floating-point The addition / subtraction operation instruction is used as the current operation instruction, and the two operands of the current opera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com