Forming method of dielectric layer

A dielectric layer and semiconductor technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as changes in the capacitance value of ultra-low-k dielectric layers, prevent k-value drift and large changes in capacitance, and avoid dielectric Influence of electric constant, effect of guaranteeing stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0031] Figure 6 to Figure 11 It is a schematic diagram of the first embodiment of forming a semiconductor device including an ultra-low-k dielectric layer according to the present invention (taking the formation of a metal wiring layer as an example). Such as Figure 6 As shown, a semiconductor substrate 100 is provided, and structures such as transistors, capacitors, and metal wiring layers are usually formed on the semiconductor substrate 100 through previous processes.

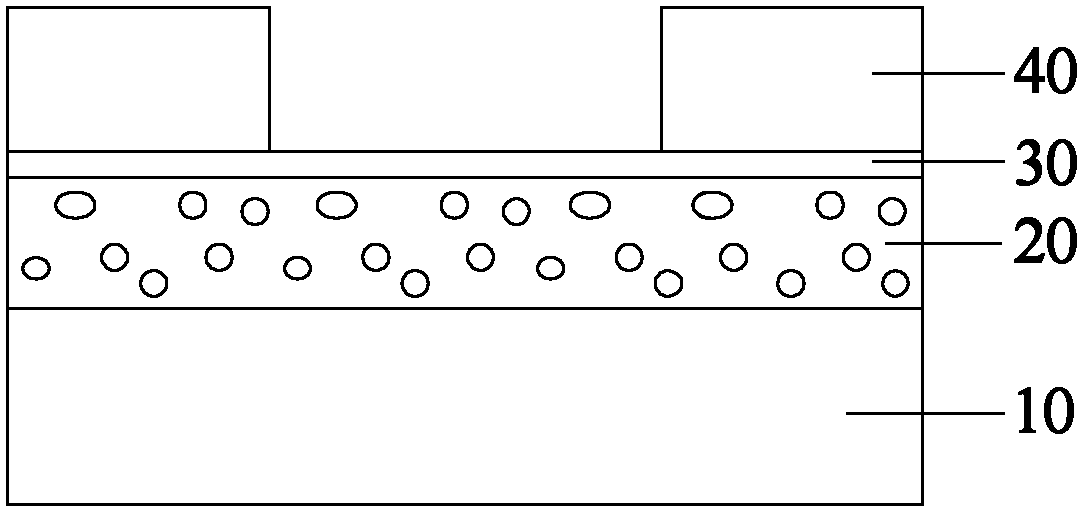

[0032] Because in the process of fabricating the metal wiring in this embodiment, the thickness of the dielectric layer to be formed is 2400 angstroms to 3000 angstroms. Therefore, using the method of this embodiment, the first layer of dielectric material 200a is first formed on the semiconductor substrate 100 by chemical vapor deposition, and the thickness of the first layer of dielectric material 200a is 800 angstroms to 1000 angstroms. Then, a first carbon treatment 300a is performed on the first lay...

no. 2 example

[0046] Figure 12 to Figure 19 It is a schematic diagram of a second embodiment of forming a semiconductor device including an ultra-low-k dielectric layer according to the present invention (taking the formation of a conductive plug of a dual damascene structure as an example). Such as Figure 12 As shown, a semiconductor substrate 1000 is provided, and structures such as transistors, capacitors, and metal wiring layers are usually formed on the semiconductor substrate 1000 through previous processes;

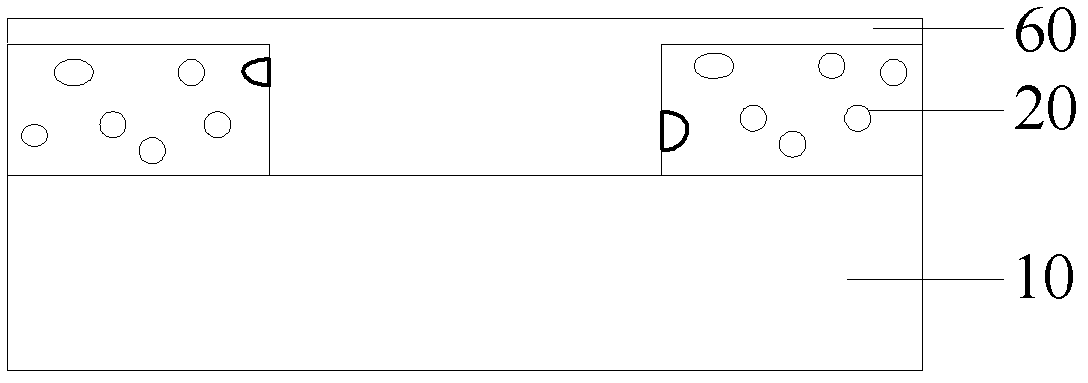

[0047] Because in the process of manufacturing the conductive plug of the dual damascene structure in this embodiment, the thickness of the dielectric layer to be formed is 3200 angstroms to 4000 angstroms. Therefore, using the method of this embodiment, the first layer of dielectric material 2000a is first formed on the semiconductor substrate 1000 by chemical vapor deposition, and the thickness of the first layer of dielectric material 2000a is 800-1000 angstroms. Then, th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com