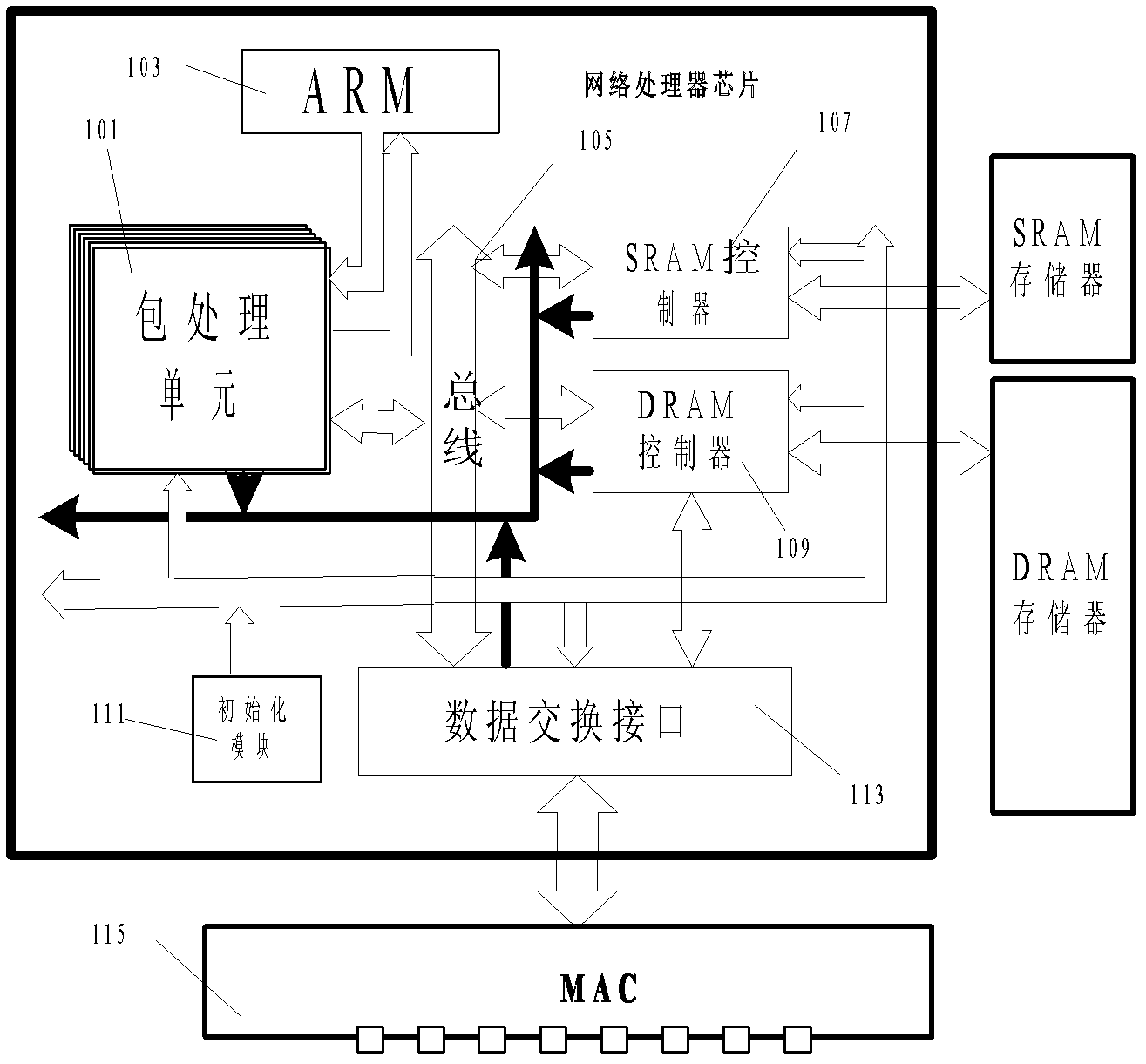

Method and system for controlling high-speed interface in multi-processor system-on-chip

A multi-core system, high-speed interface technology, applied in transmission systems, digital transmission systems, instruments, etc., can solve the problems of slow processing units, indeterminate states, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The present invention is shown by way of example, but not limitation, in the accompanying drawings, in which like reference numbers represent similar structures.

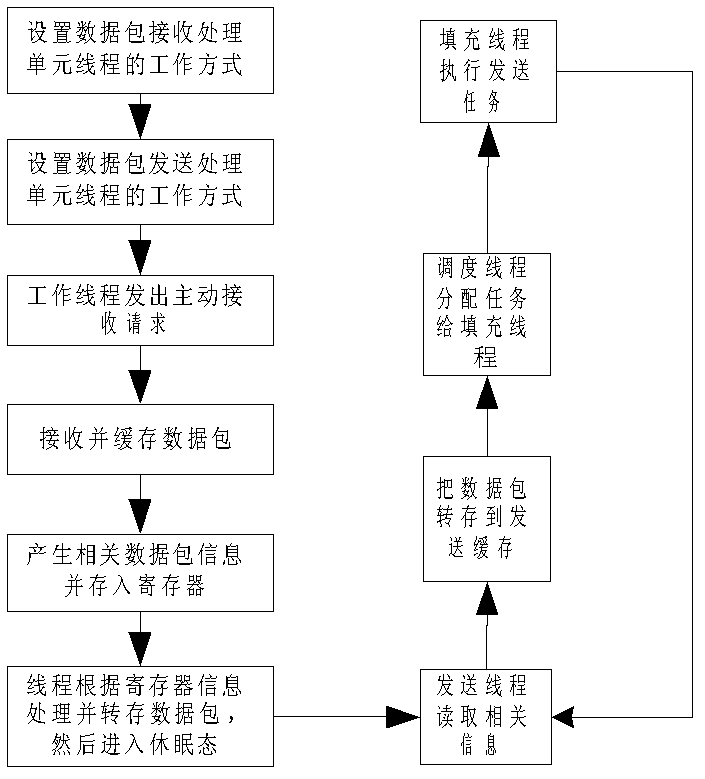

[0055] Below in conjunction with specific embodiment, the present invention is described in further detail:

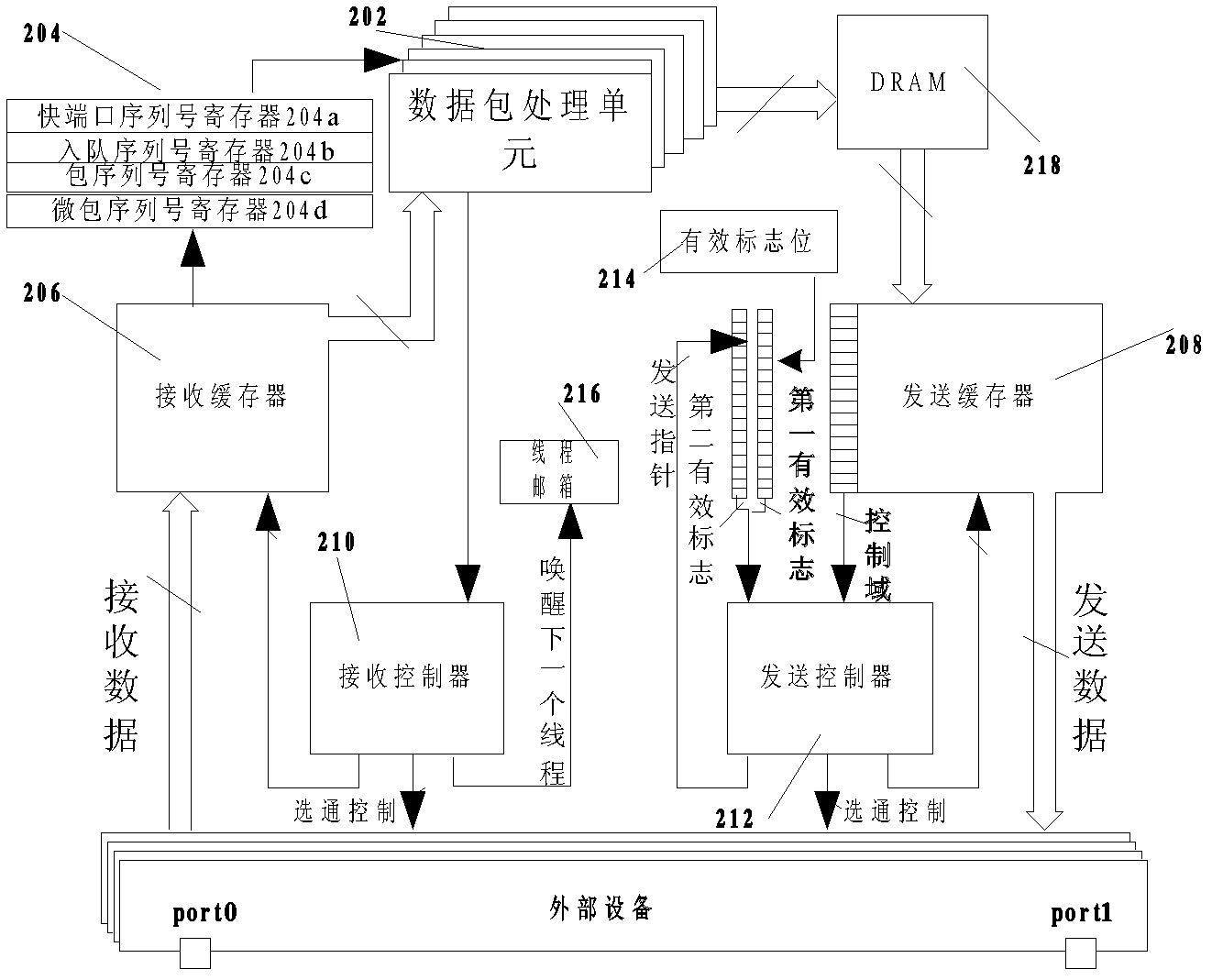

[0056] refer to figure 2 , is the control system of the present invention, comprising packet processing unit 202, packet information register 204, receiving buffer 206, sending buffer 208, receiving controller 210, sending controller 212, valid flag 214, thread mailbox 216 and Large-capacity dynamic random access memory DRAM218, wherein:

[0057] The data packet processing unit 202, as the core element of network processor packet processing, frequently exchanges data with other units. In this embodiment, the data packet processing unit includes four data packet receiving processing units and two data packet sending processing units. The six data packet processing units, as the main control end, are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com