FPGA task scheduling method based on condition preemption

A task scheduling and task technology, applied in the direction of multi-programming devices, etc., can solve the problem of high complexity, achieve the effect of low scheduling complexity and reduce waiting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

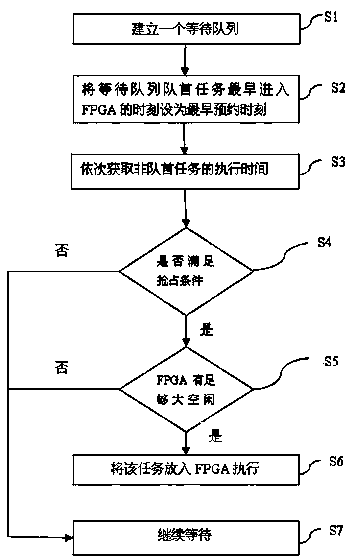

[0022] Such as figure 1 Shown, the specific implementation steps of the method of the present invention are as follows:

[0023] 1) Create a waiting queue, which is used to place tasks waiting to enter the FPGA;

[0024] 2) Set the time when the head task of the waiting queue first enters the FPGA as the earliest reservation time;

[0025] 3) Obtain non-team leader tasks sequentially, and obtain their execution time;

[0026] 4) Judging whether they meet the preemption condition: current time + task execution time ≤ earliest reservation time of the team leader task. If it is satisfied, skip to 5), if not, skip to 7);

[0027] 5) Judging whether there is enough free space in the FPGA at this moment to allow the task to be placed, if so, skip to 6), otherwise skip to 7);

[0028] 6) The task is put into the FPGA for execution prior to the team leader task;

[0029] 7) The task continues to wait.

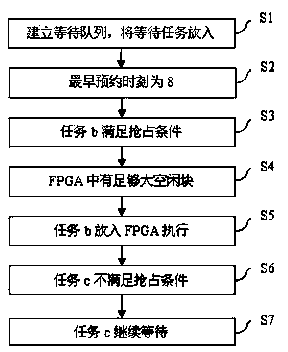

[0030] Such as figure 2 As shown, an example of an FPGA task scheduling me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com