Multi-clock-ring based method for avoiding clock jitter in switching process

A technology of clock switching and master clock, which is applied in multiplexing communication, data exchange network, time division multiplexing system, etc. It can solve the problems of time jitter, inconsistency between master clock A and B, accidents, etc., and achieve improved Reliability and stability, smooth switching process, avoiding the effect of time jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

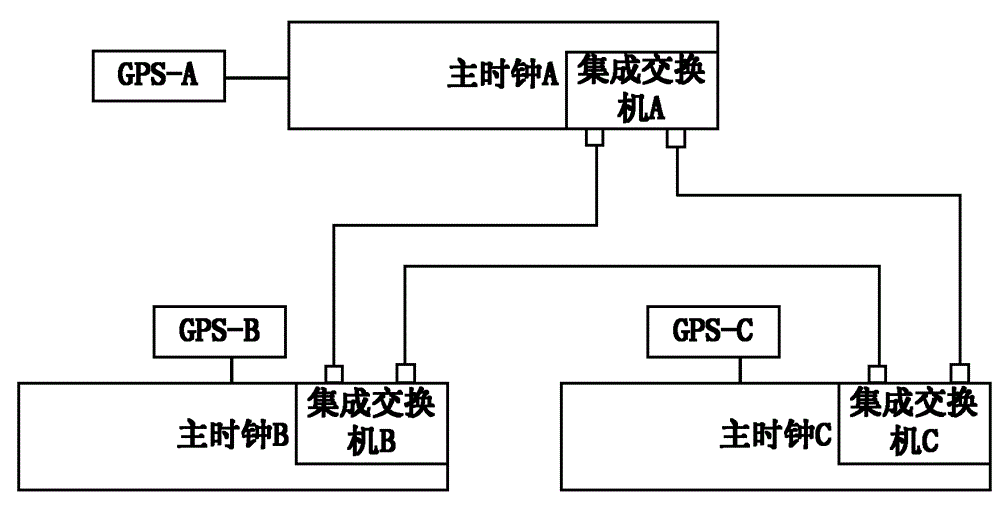

[0026] In this embodiment, three main clocks are used to form a clock ring as an example to describe the following.

[0027] The connection diagram of the multi-clock ring composed of three main clocks is as follows: image 3 As shown, a ring network structure is formed among master clock A, master clock B and master clock C, and each master clock is provided with a micro-switch for sending and receiving calibration time messages. The method for preventing clock switching jitter based on multiple clock rings of the present invention comprises the following steps:

[0028] In the first step, a ring network structure is formed among master clock A, master clock B and master clock C;

[0029] In the second step, the three master clocks (master clock A, master clock B, and master clock C) all start the topology discovery protocol (using rapid spanning tree protocol) on the ring network port to discover the ring network situation and finally determine one of them. Lines are disco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com