Carbon silicon-germanium silicon heterojunction 1T-DRAM (Single Transistor Dynamic Random Access Memory) structure on insulator and forming method thereof

A 1T-DRAM, insulator technology, applied in the manufacturing of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of small signal current, limited increase in hole barrier, little increase in signal current and retention time, etc. The effect of operating voltage, increasing output current balance, and increasing signal margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

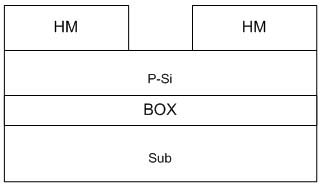

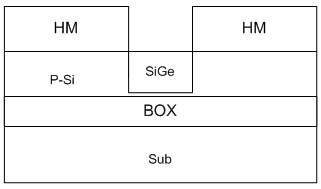

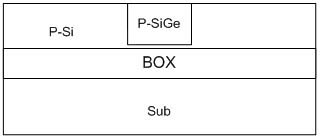

[0041] The present invention provides a carbon silicon-germanium silicon heterojunction 1T-DRAM structure, comprising: a semiconductor substrate, a buried oxide layer, the buried oxide layer covers the semiconductor substrate; a P-type silicon layer, the The P-type silicon layer is covered on the buried oxide layer, and the P-type silicon layer is provided with NMOS devices separated by STI, wherein the channel in the NMOS device is P-type SiGe.

[0042] The present invention will be further described below through the examples, so that the content of the present invention can be better understood, but the following examples do not limit the protection scope of the present invention.

[0043] The silicon-on-insulator silicon-germanium heterojunction 1T-DRAM structure provided by the present invention is formed by the following method.

[0044]A hard mask layer is deposited on the formed SOI wafer, and the hard mask layer is generally silicon nitride material. Carrying out pho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com