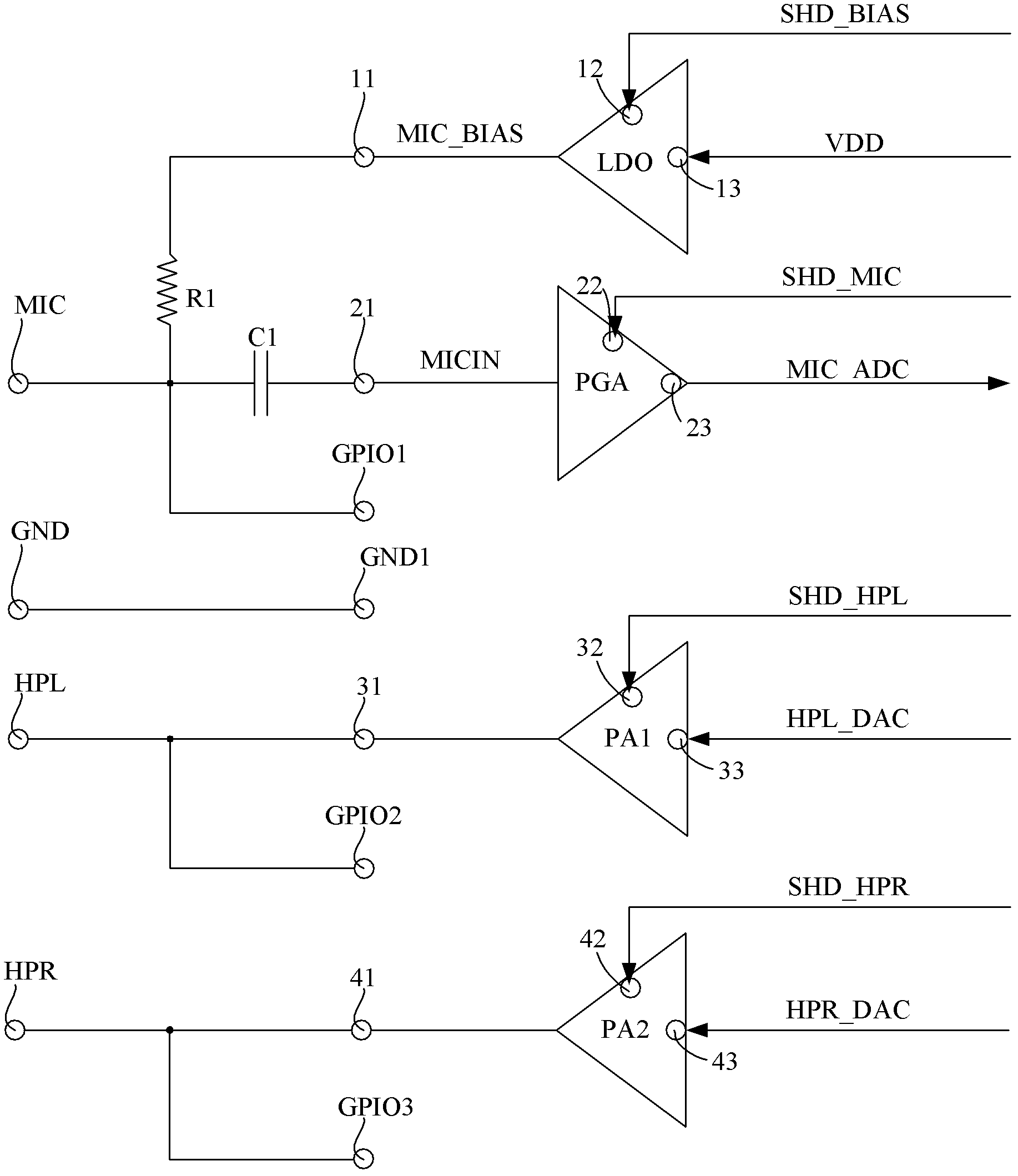

Headset interface and GPIO (General Purpose Input/Output) interface multiplex circuit structure

A technology of interface multiplexing and circuit structure, applied in transducer circuits, stereo circuit arrangements, electrical components, etc., to achieve the effect of expanding functions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

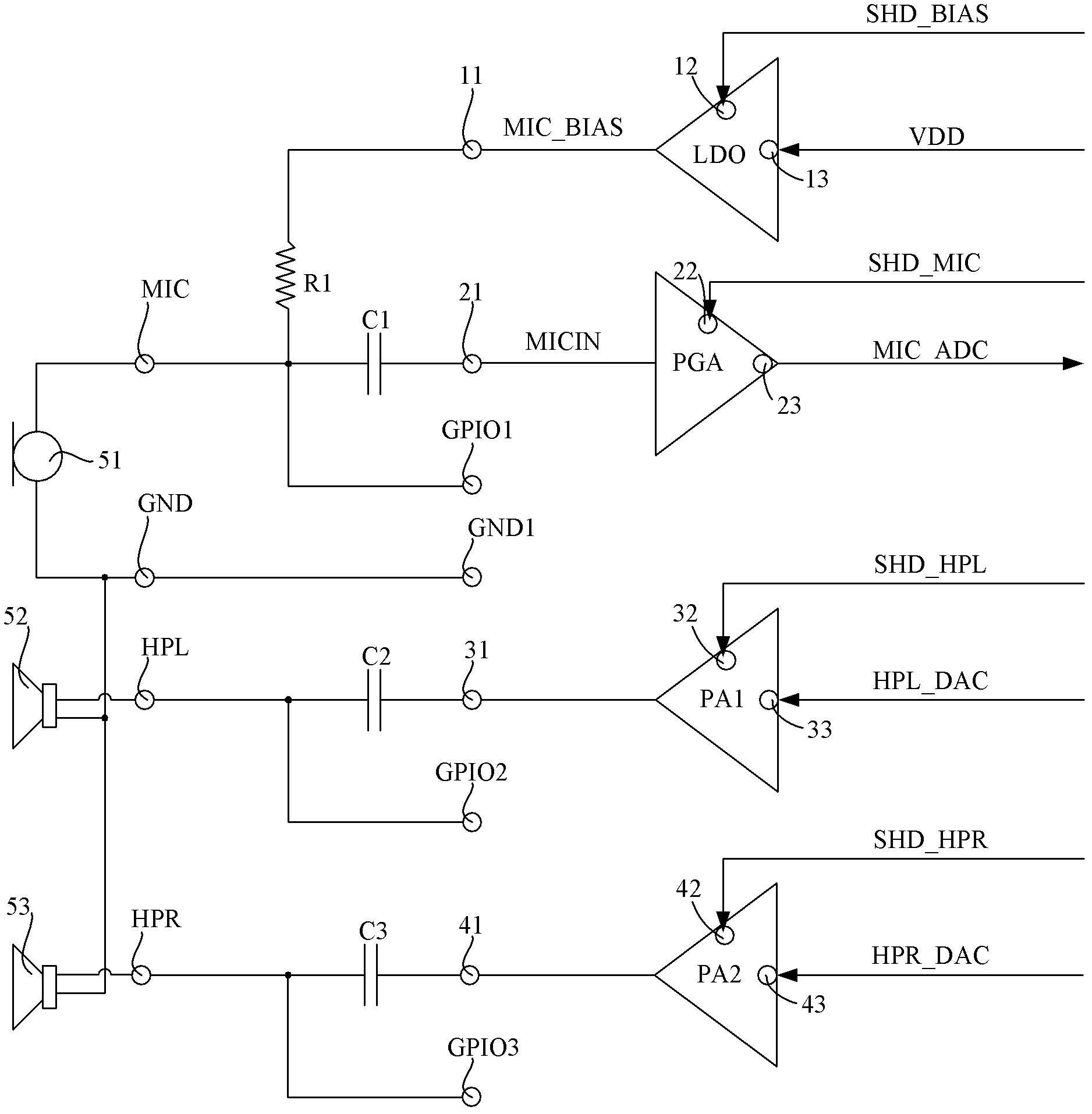

Embodiment 1

[0039] see figure 2 In this embodiment, the multiplexing circuit structure of the headset interface and the GPIO interface is configured as a traditional headset interface. The output terminal 31 of the first power amplifier PA1 is connected to the second capacitor C2 and then connected to the left channel earphone interface HPL, and the second general input and output interface GPIO2 is connected to the left channel earphone interface HPL; The output terminal 41 of the second power amplifier PA2 is connected with the third capacitor C3 and connected with the right channel earphone interface HPR, and the third general input and output interface GPIO3 is connected with the right channel earphone interface HPR; the microphone 51 is connected to the right channel earphone interface HPR. Between the microphone interface MIC and the ground port GND, the left earphone 52 is connected between the left channel earphone interface HPL and the ground port GND, and the right earphone 53 ...

Embodiment 2

[0041] see image 3 In this embodiment, the headset interface and GPIO interface multiplexing circuit structure is configured as a GPIO general data interface. The output terminal 31 of the first power amplifier PA1 is connected to the fourth capacitor C4 and then connected to the left channel earphone interface HPL, and the second general input and output interface GPIO2 is connected to the left channel earphone interface HPL; The output terminal 41 of the second power amplifier PA2 is connected to the fifth capacitor C5 and then connected to the right channel earphone port HPR, and the third general input and output interface GPIO3 is connected to the right channel earphone port HPR. The first control signal SHD_BIAS, the second control signal SHD_MIC, the third control signal SHD_HPL, and the fourth control signal SHD_HPR sent by the host register are all at high level. Correspondingly, the low dropout linear regulator LDO and The programming gain amplifier PGA, the first ...

Embodiment 3

[0043] see Figure 4 In this embodiment, the multiplexing circuit structure of the headset interface and the GPIO interface is configured as an I2C interface. The first control signal SHD_BIAS, the second control signal SHD_MIC, the third control signal SHD_HPL, and the fourth control signal SHD_HPR sent by the host register are all at high level. Correspondingly, the low dropout linear regulator LDO and The programming gain amplifier PGA, the first power amplifier PA1 and the second power amplifier PA2 are all disconnected, and are externally shown as a high-impedance state, while the first general-purpose input and output interface GPIO1, the second general-purpose input-output interface GPIO2 and the third general-purpose input The output interface GPIO3 forms an I2C interface through proper configuration. When configuring these three general-purpose input and output interfaces, they can be rotated. Figure 4 Only one of the possible configurations is shown. Such as Fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com