Image mosaic processor on basis of FPGA (Field Programmable Gata Array) and image mosaic method

An image mosaic and processor technology, applied in image communication, instruments, static indicators, etc., can solve the problems of bandwidth bottleneck, lack of processing capacity, and small development space, etc., to meet application requirements, avoid signal loss, and improve processing The effect of response speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

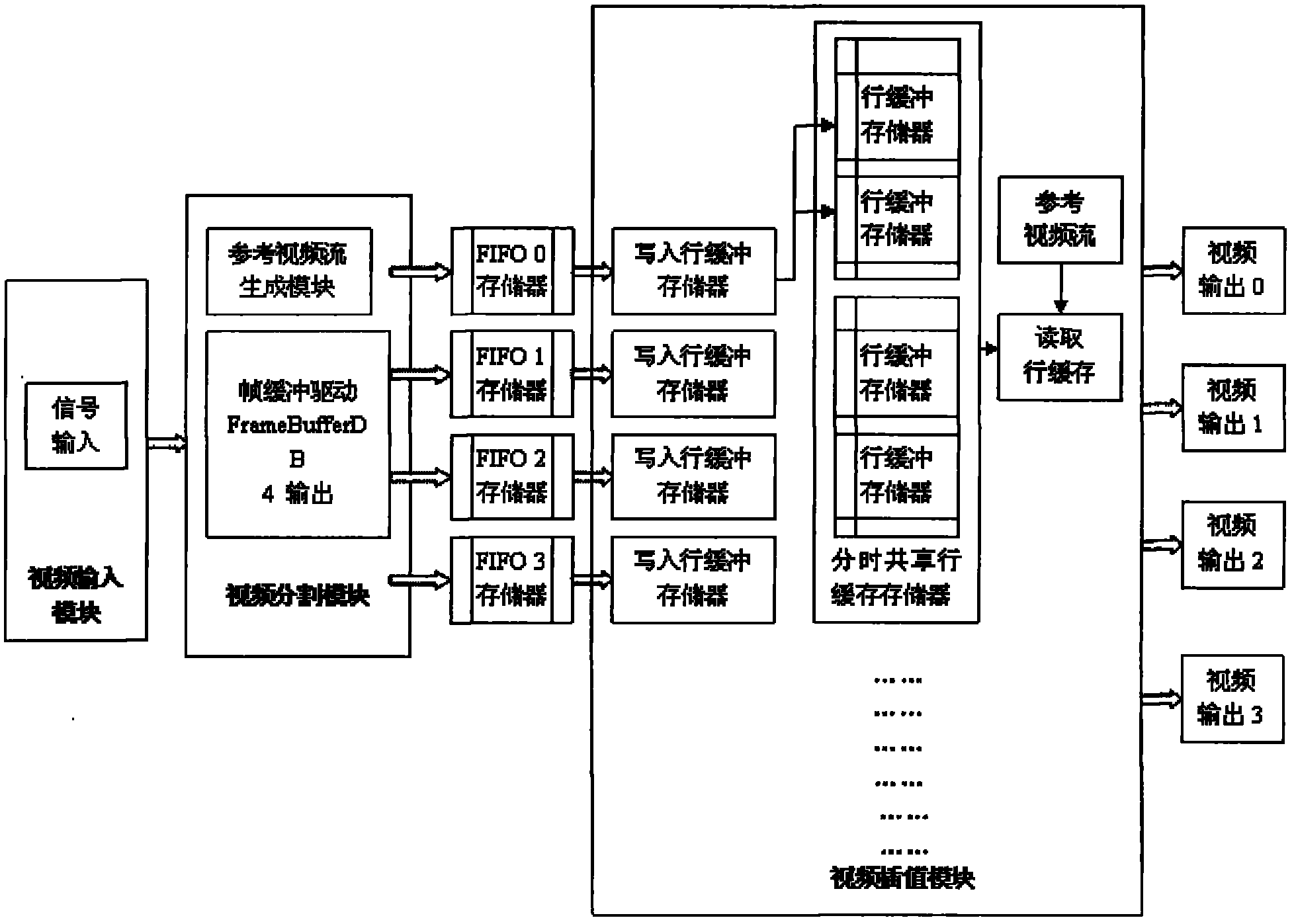

[0023] Such as figure 1 and figure 2 As shown, the present invention provides an FPGA-based image splicing processor, which is characterized by including a set of DVI digital decoding circuits, a set of FPGA digital video processing circuits, and a set of output interface circuits, wherein the external digital signal and The DVI digital decoding circuit is connected to decode the digital video signal in the form of the smallest converted differential signal, and the obtained video pixel information stream is directly sent to the FPGA digital video processing circuit. After the image processing algorithm, the signal is encoded and processed to obtain the minimum The digital video signal of the differential signal is output to the splicing wall display through the output interface circuit.

[0024] The output interface circuit includes a set of DVI digital encoding circuits and a set of DVI interfaces. The digital video signal output by the FPGA digital video processing circuit is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com