Welding disc and silicon-on-insulator (SOI) device with same

A technology of silicon-on-insulator and pads, which is applied to electric solid-state devices, semiconductor devices, semiconductor/solid-state device parts, etc., can solve the problem that it is not easy to form shallow trench isolation layers, the shallow trench isolation layer has limited height, and the spacing is enlarged. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

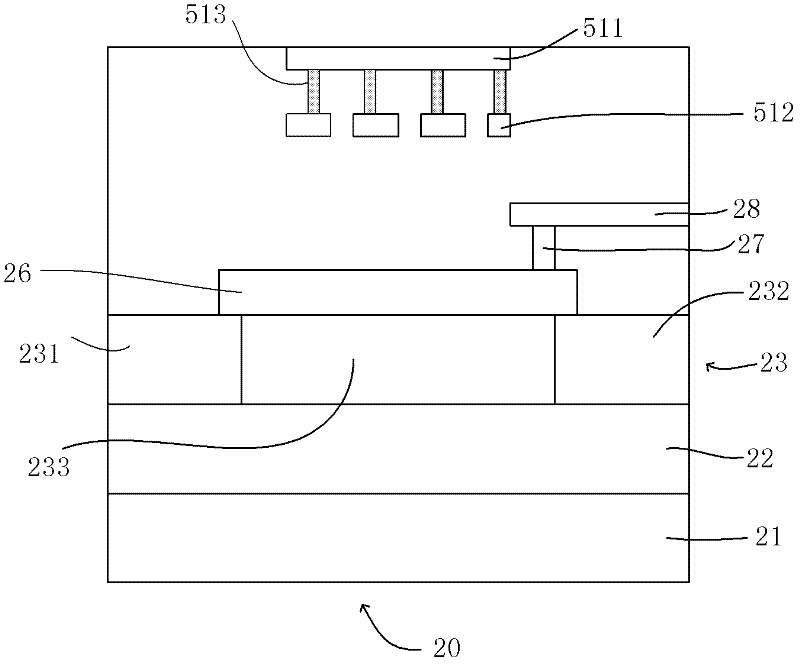

[0044] Such as image 3 As shown, the silicon-on-insulator device includes a silicon-on-insulator substrate 20, and the silicon-on-insulator substrate 20 includes a silicon substrate 21, a buried oxide layer 22 formed on the silicon substrate, and a silicon layer 23 formed on the buried oxide layer, The silicon layer 23 can be used to form various semiconductor devices. Wherein, a source region 231 , a drain region 232 of the transistor and an STI isolation region 233 for isolating the source region and the drain region are formed on the silicon layer 23 . The source region 231 and the drain region 232 are source regions or drain regions of two different transistors in a silicon-on-insulator device.

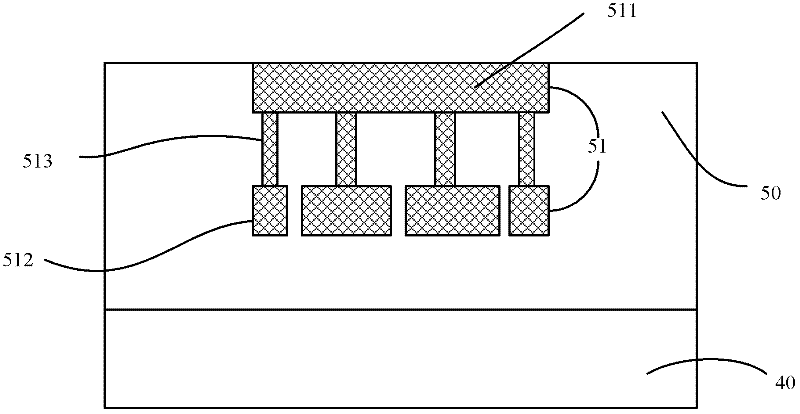

[0045] The silicon-on-insulator device further includes the above-mentioned pad, which includes several pad metal layers, the pad metal layer 512 close to the semiconductor substrate is divided into several parts separated from each other, the pad metal layer 512 close to the se...

Embodiment 2

[0052] Such as Figure 4 As shown, the silicon-on-insulator device includes a silicon-on-insulator substrate 20, and the silicon-on-insulator substrate 20 includes a silicon substrate 21, a buried oxide layer 22 formed on the silicon substrate, and a silicon layer 23 formed on the buried oxide layer, Silicon layer 23 can be used to form various devices. Specifically, a source region 231 , a drain region 232 and an STI isolation region 233 for isolating the source region and the drain region are formed on the silicon layer. The source region 231 and the drain region 232 are the source regions or drain regions of two different transistors in the silicon-on-insulator device, and the STI isolation region 233 is formed using a conventional shallow trench isolation process, including a trench formed in the silicon-on-insulator substrate. trench, trench fill oxide, which may be silicon oxide. The bottom of the STI isolation region 233 extends to the interface between the silicon su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com