High spurious-free-dynamic-range (SFDR) multichannel time staggering successive approximation type analog to digital converter

An analog-to-digital converter, successive approximation technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve the problems of quantization error, affecting linearity, etc., and achieve the effect of improving linearity and randomization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

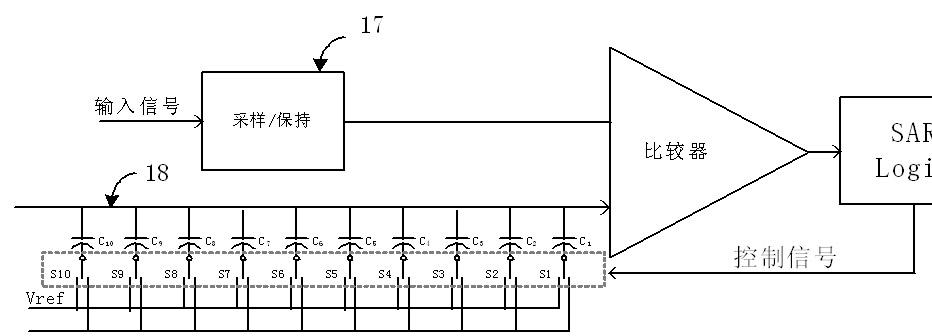

[0023] The implementation method of the circuit will be further explained in conjunction with the diagram below:

[0024] The capacitor pool module 21 is composed of the original capacitor 19 for each channel and a set of redundant capacitor arrays.

[0025] Image 6 It is the specific implementation method of the pseudo-random number generator 23, which adopts the improved linear feedback shift register (LFSR) method, which has a simple structure, is easy to implement, and has a relationship between the period of the random number and the number of registers that grow exponentially . When necessary, the cycle period of the pseudo-random number can be increased only by increasing the number of shift registers at each stage. Under the control of the clock CLK1 22, select the required output node from the PRG 23, and then connect each randomized capacitor to each channel through a decoder 24 as the capacitor for each sampling and quantization array.

[0026] The improved ove...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com