Substrate processing system and substrate processing method

A substrate processing system and processing scheme technology, applied in the directions of transportation and packaging, conveyor objects, electrical components, etc., can solve problems such as inability to perform exposure processing, poor equipment, and failure to solve problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

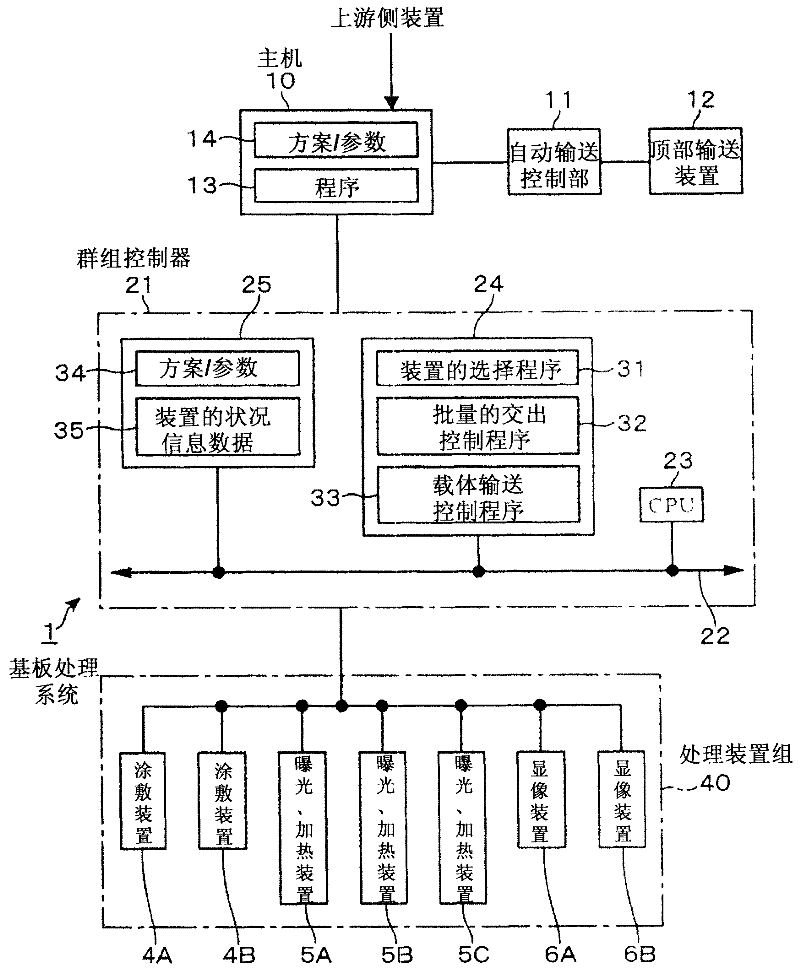

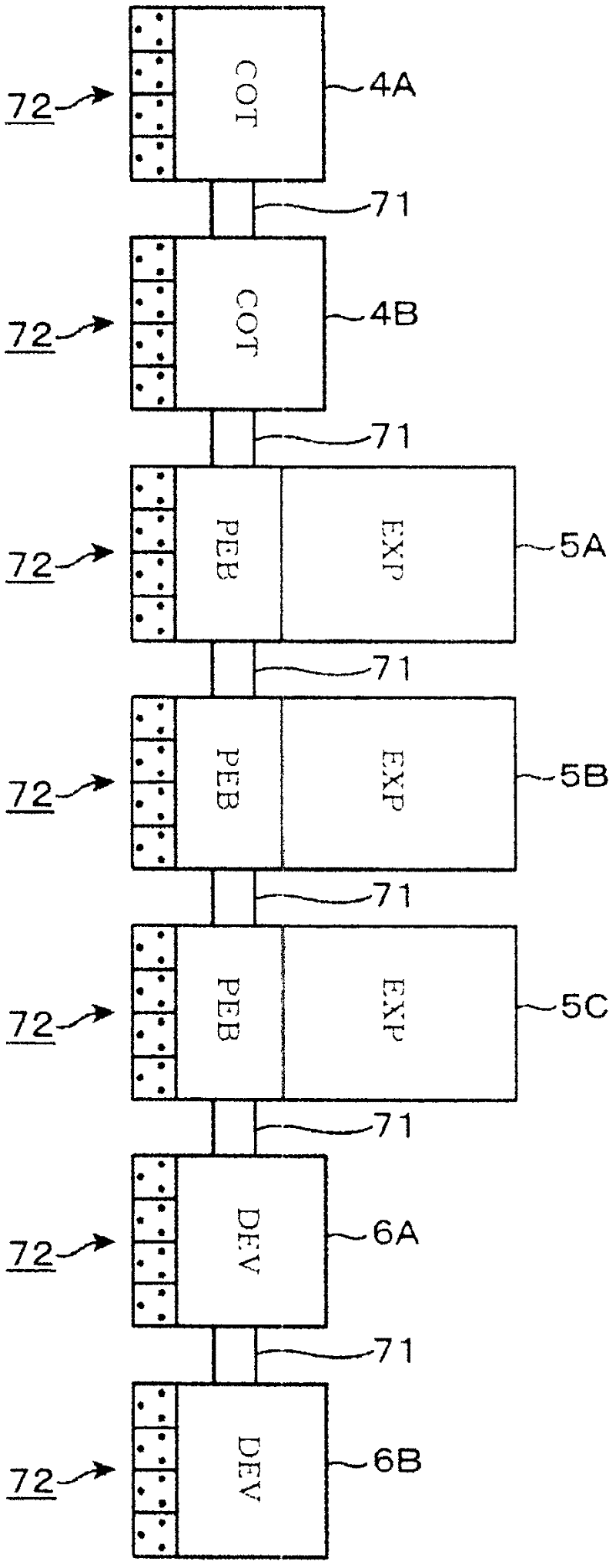

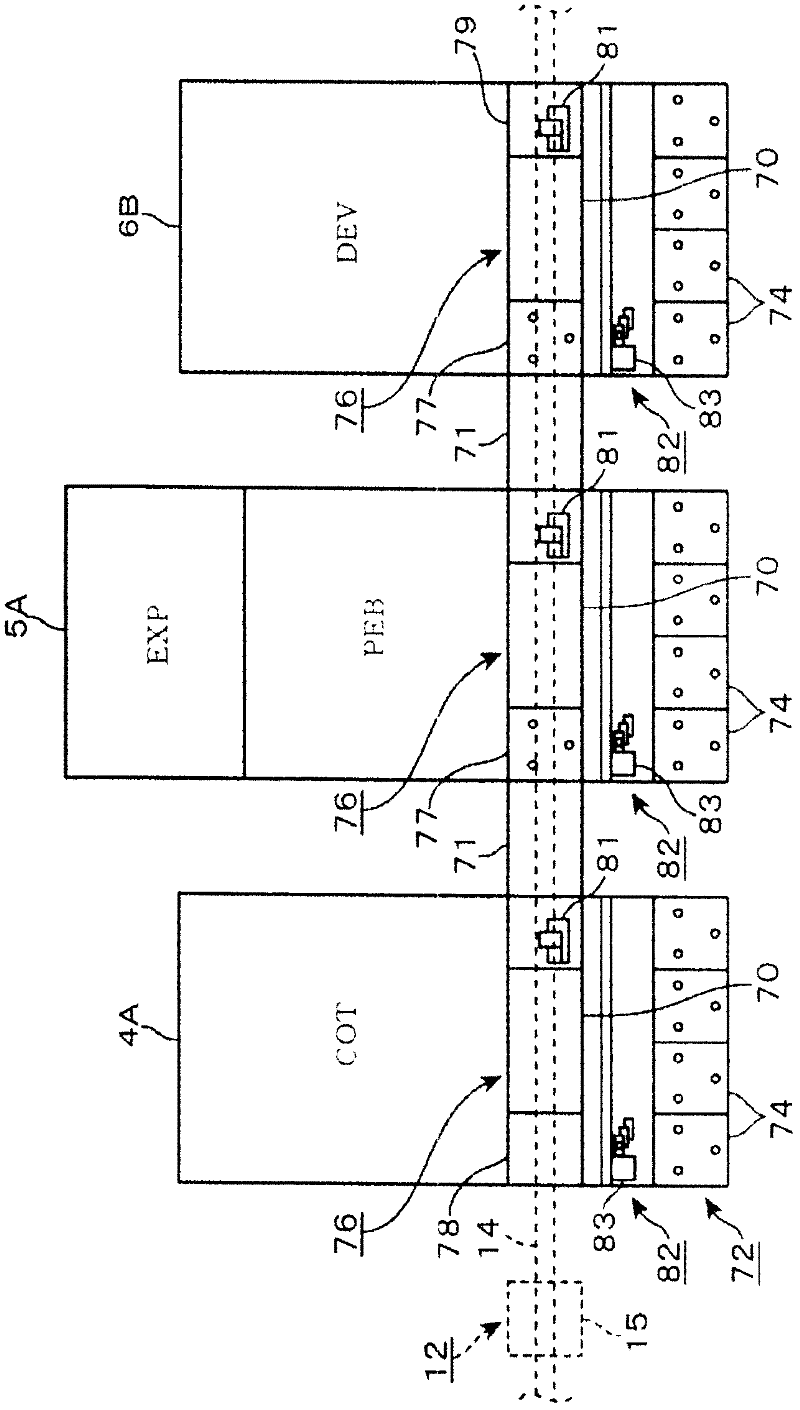

[0102] figure 1 It is an overall configuration diagram of a substrate processing system 1 as an embodiment of the present invention. The substrate processing system 1 is composed of a group of processing devices 40, and the carrier C is transported between the processing devices to form a resist pattern on the wafer W. A plurality of wafers W of the same type are accommodated in one carrier C, and the wafers W of the same type are called a lot. The substrate processing system 1 includes a host computer 10 , a group controller 21 , a top transport device 12 , and the processing device group 40 described above. The processing device group 40 includes: coating devices 4A, 4B; exposure and heating devices 5A to 5C; and developing devices 6A, 6B.

[0103] The main machine 10 is connected to the top conveying device 12 through the automatic conveying control unit 11 . In addition, the host computer 10 is connected to the group controller 21 and connected to the processing device ...

no. 2 approach

[0152] Figure 13 The layout of the substrate processing system 121 of the second embodiment is shown. The coating devices 4A, 4B, exposure devices 5A, 5B, developing devices 6A, 6B, and inspection devices 7A, 7B are connected in this order.

[0153] The inspection devices 7A and 7B include an inspection module for inspecting the surface state of the developed wafer W, and the inspection devices 7A and 7B are the same as the coating device 4A except that the above-mentioned inspection module is mounted on the processing station 101 instead of the coating module. to constitute. The developed wafer W is inspected by the inspection device 7A or 7B. The carrier C is conveyed from the coating device 4A side to the inspection device 7B side, and a common carry-out stack 79 is provided at the carrier station 72 of the inspection device 7B.

[0154] In this substrate processing system 121, similarly to the substrate processing system 1, maintenance information, the processing statu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com