Polycrystalline Si1-xGex/metal parallel covering double-gate strained SiGe-on-insulator (SSGOI) n metal oxide semiconductor field effect transistor (MOSFET) device structure

A technology of device structure and double-gate structure, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as growth, low thermal conductivity, and self-heating

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

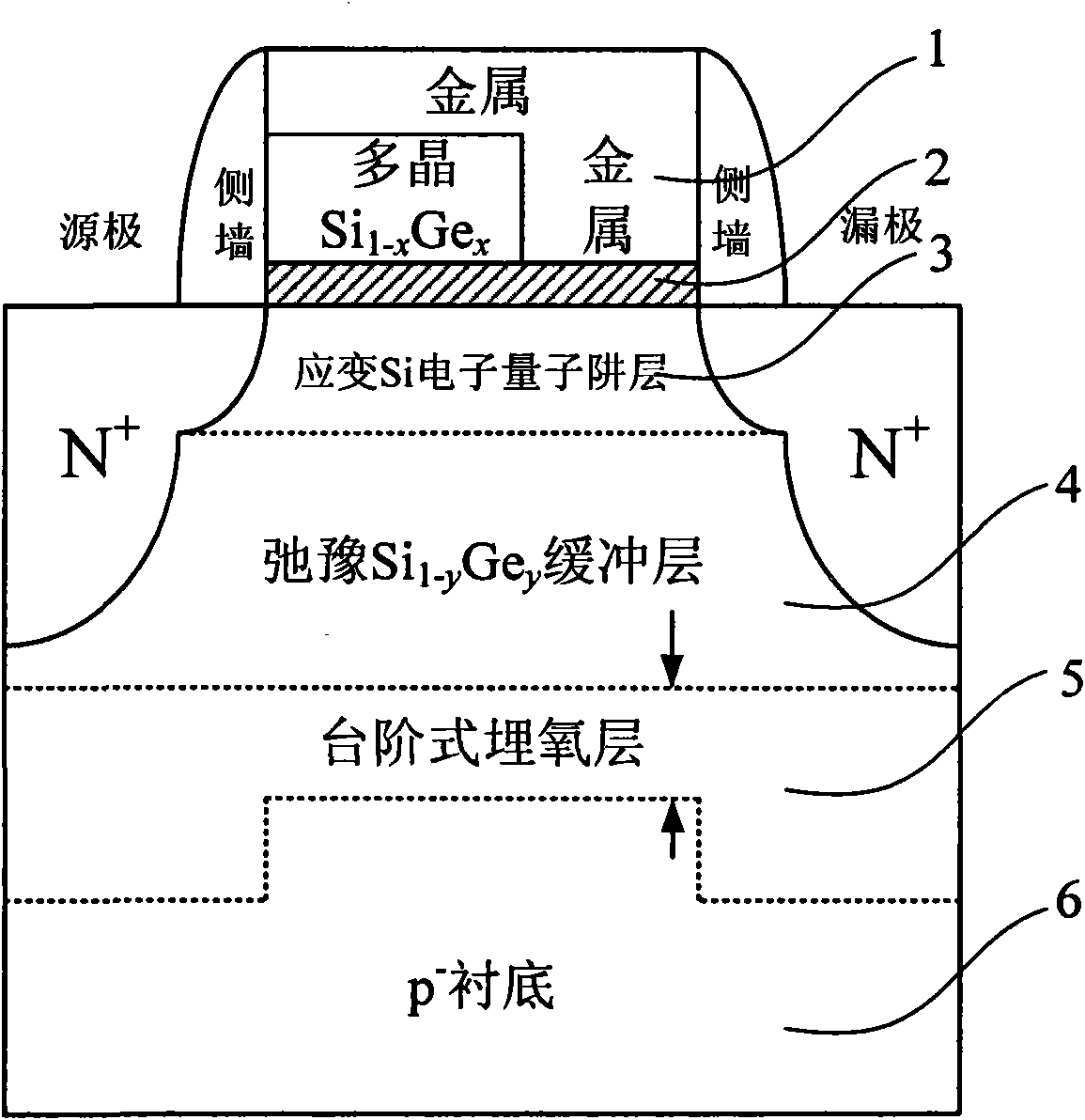

[0029] Such as figure 1 As shown, the novel polycrystalline Si of the present invention 1-x Ge x / Metal side-by-side covered double-gate stepped buried oxide SSGOI nMOS-FET device structure includes: polycrystalline Si 1-x Ge x / Metal parallel covering double gate structure 1; gate insulating layer 2; intrinsic (or p - doped) strained Si electron quantum well layer 3; p-doped relaxed Si 1-y Ge y buffer layer 4; stepped buried oxide layer 5; p - Doped single crystal Si(100) substrate 6, the p - Doped single crystal Si(100) substrate relaxes Si by p 1-y Ge y The buffer layer, the p-relaxation SiGe graded layer and the single crystal Si are composed of three parts (such as image 3 shown).

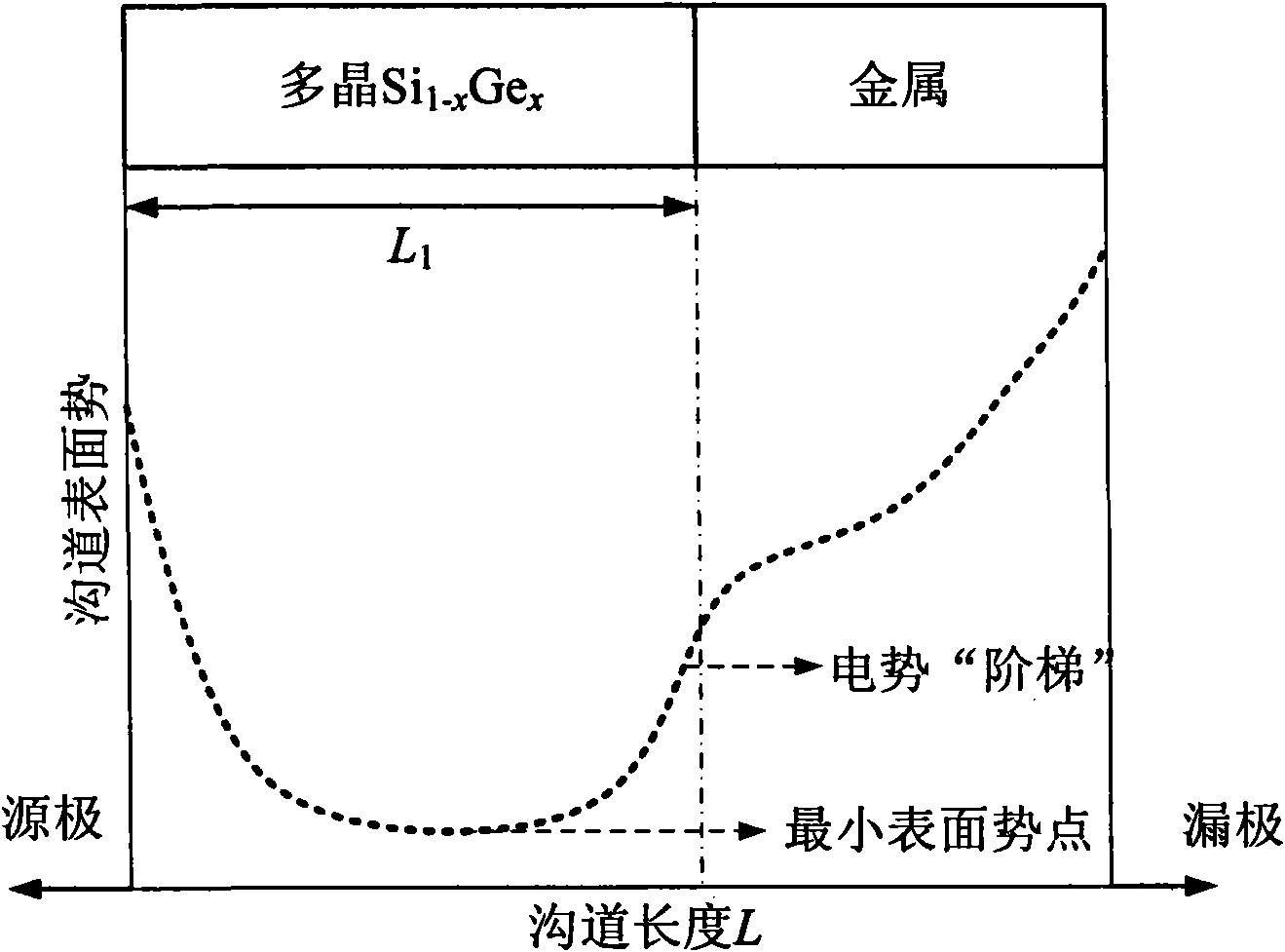

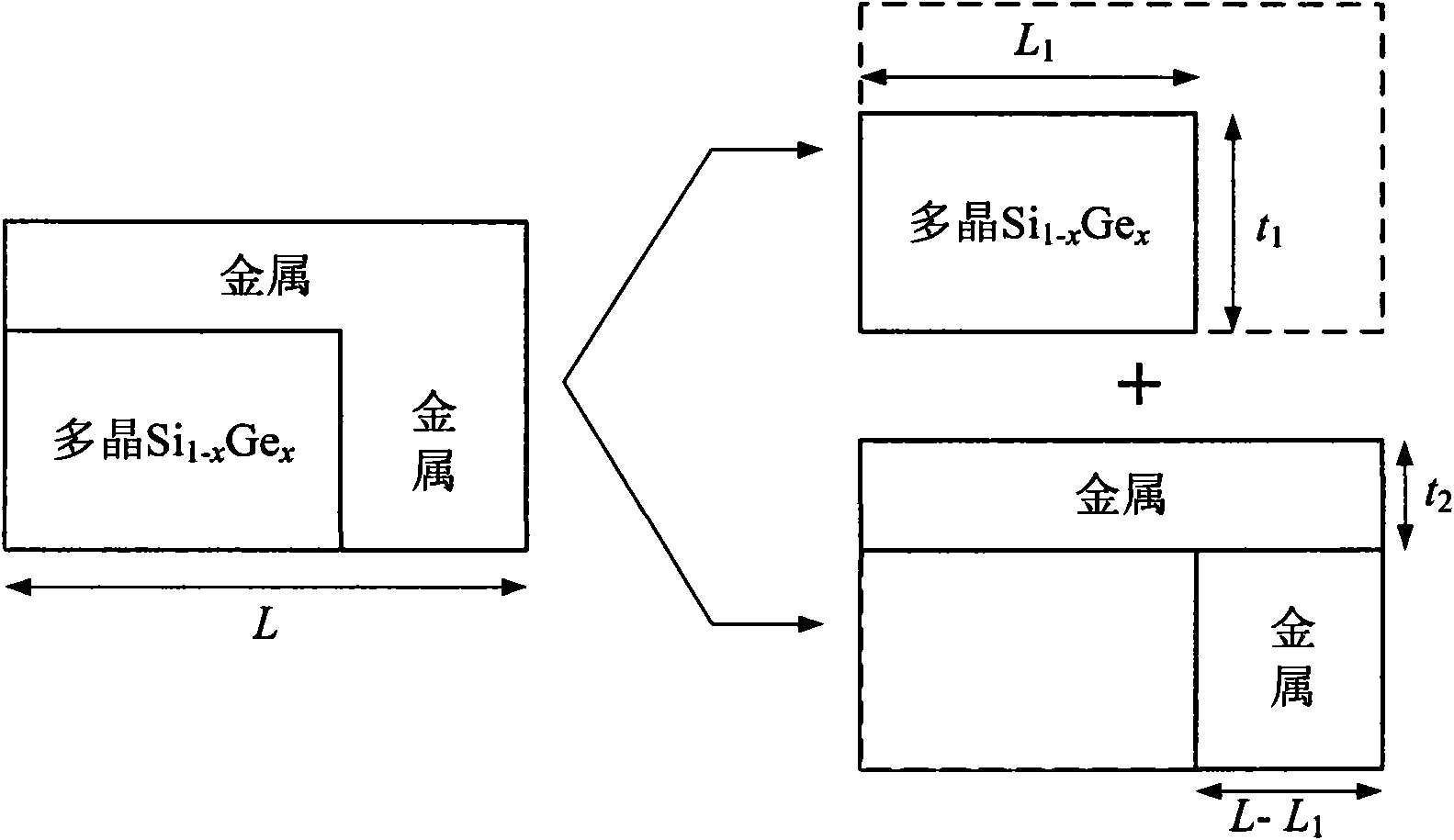

[0030] Polycrystalline Si 1-x Ge x / metal side-by-side covered double gate structure 1 including polysilicon 1-x Ge x gate and metal gate, and polysilicon 1-x Ge x The gate is completely covered by the metal gate, that is, polysilicon 1-x Ge x The gate is completely covere...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com