Electrostatic protection structure

A technology of electrostatic protection and resistance, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of occupying chip area and increasing chip cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

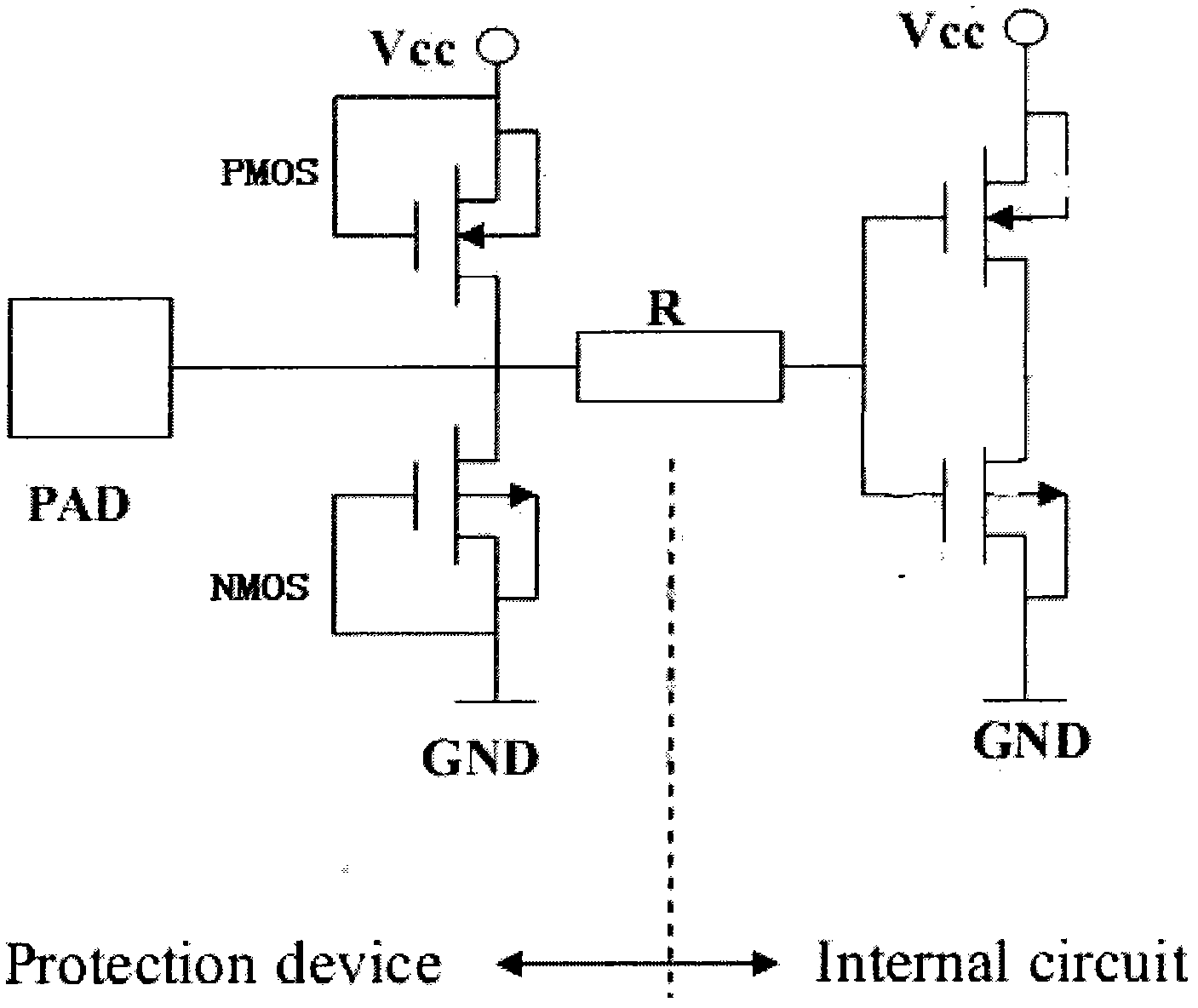

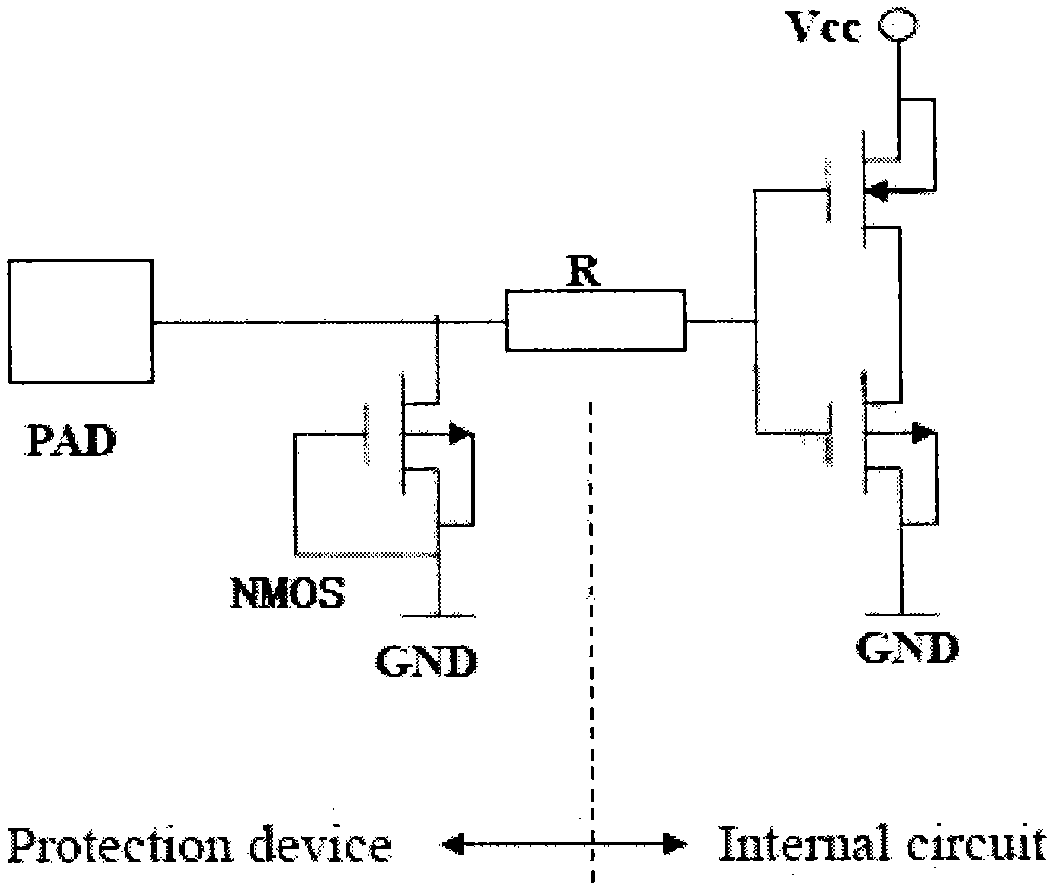

[0021] figure 1 For the circuit diagram of the prior art, electrostatic protection is performed by connecting a PMOS transistor and an NMOS transistor. figure 2 It is a circuit diagram of an embodiment of the present invention. The gate terminal, the P-type substrate and the source terminal of the NMOS transistor are connected and grounded, and the drain terminal is connected to the PAD; one end of the resistor is connected to the PAD, and the other end is the output terminal of the electrostatic protection structure, which is connected to the internal circuit. . Compared with the prior art, the present invention obviously omits one PMOS transistor and greatly reduces the chip area.

[0022] In order to further reduce the chip area without affecting the effect of electrostatic protection, the present invention further improves the layout design. Figure 4 For the layout of the NMOS tube, the distance from the through hole at the source end to the gate end is 1 μm, and the d...

Embodiment 2

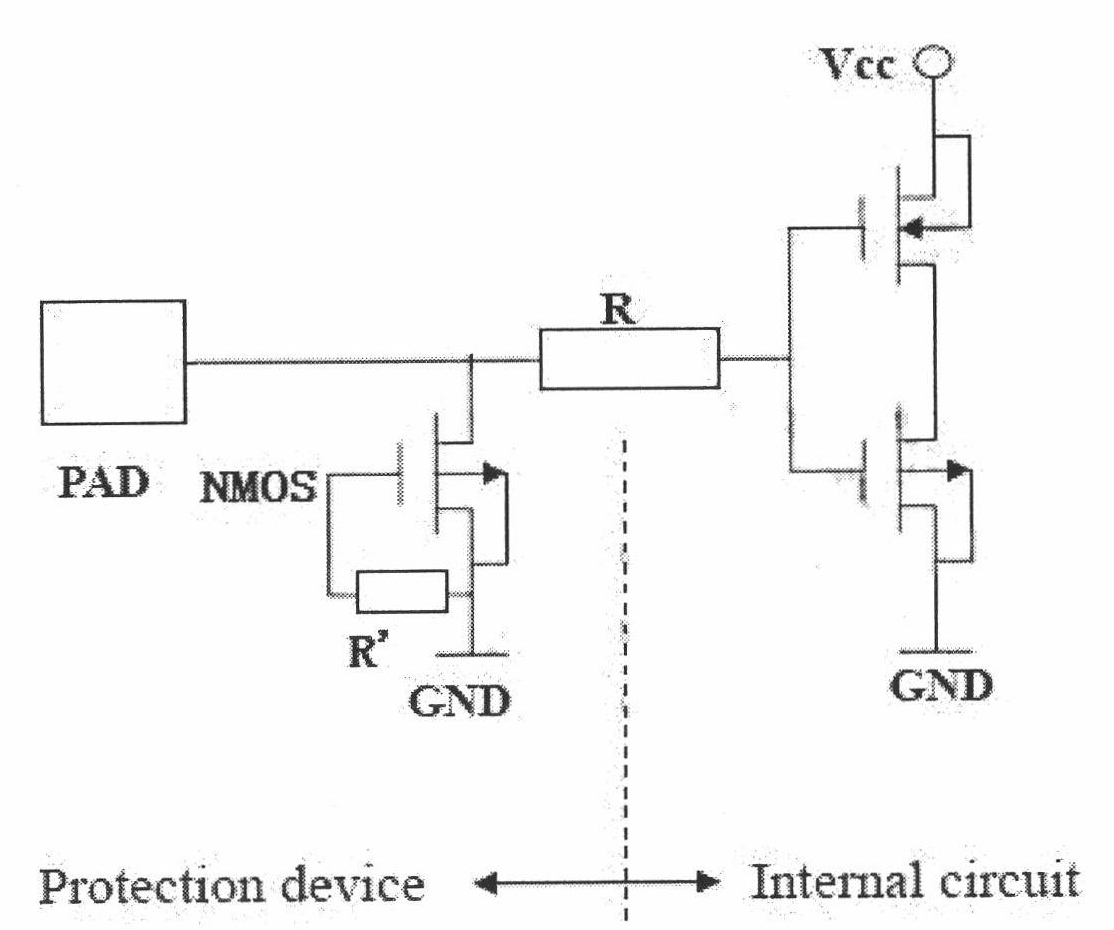

[0024] image 3 It is a circuit diagram of another embodiment of the present invention. The structure and principle of this embodiment are basically the same as those of the first embodiment. The difference is that another resistor R' is added between the gate terminal of the NMOS transistor and the ground. The reason is that not every NMOS transistor will be turned on at the same time when ESD occurs, so the effective withstand voltage of the ESD protection circuit is determined by several NMOS transistors that start to conduct. Adding another resistor R' between the gate terminal of the NMOS transistor and the ground can effectively avoid this situation.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com