Ultra-low voltage nand gate circuit

A NOT gate circuit, ultra-low voltage technology, applied in the field of ultra-low voltage NAND gate circuit, to achieve the effect of simple structure, easy design and good symmetry

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

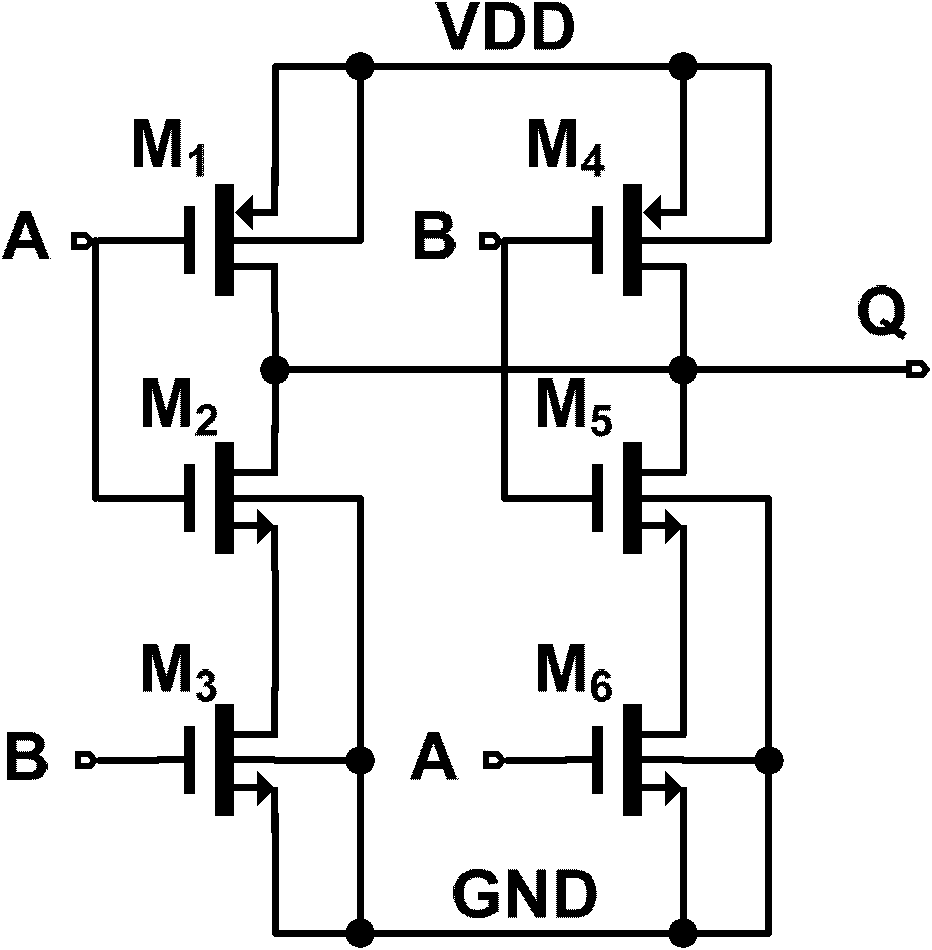

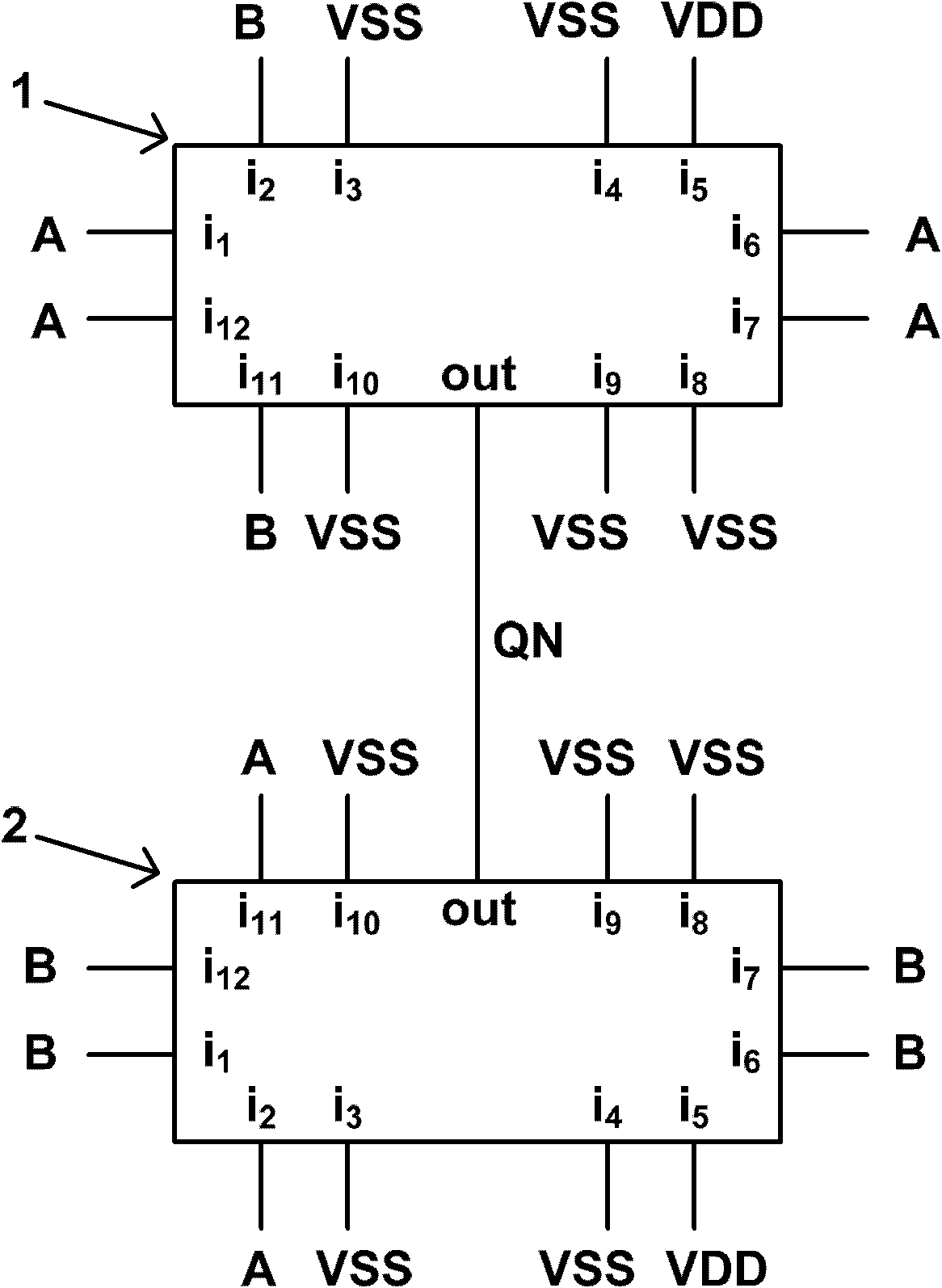

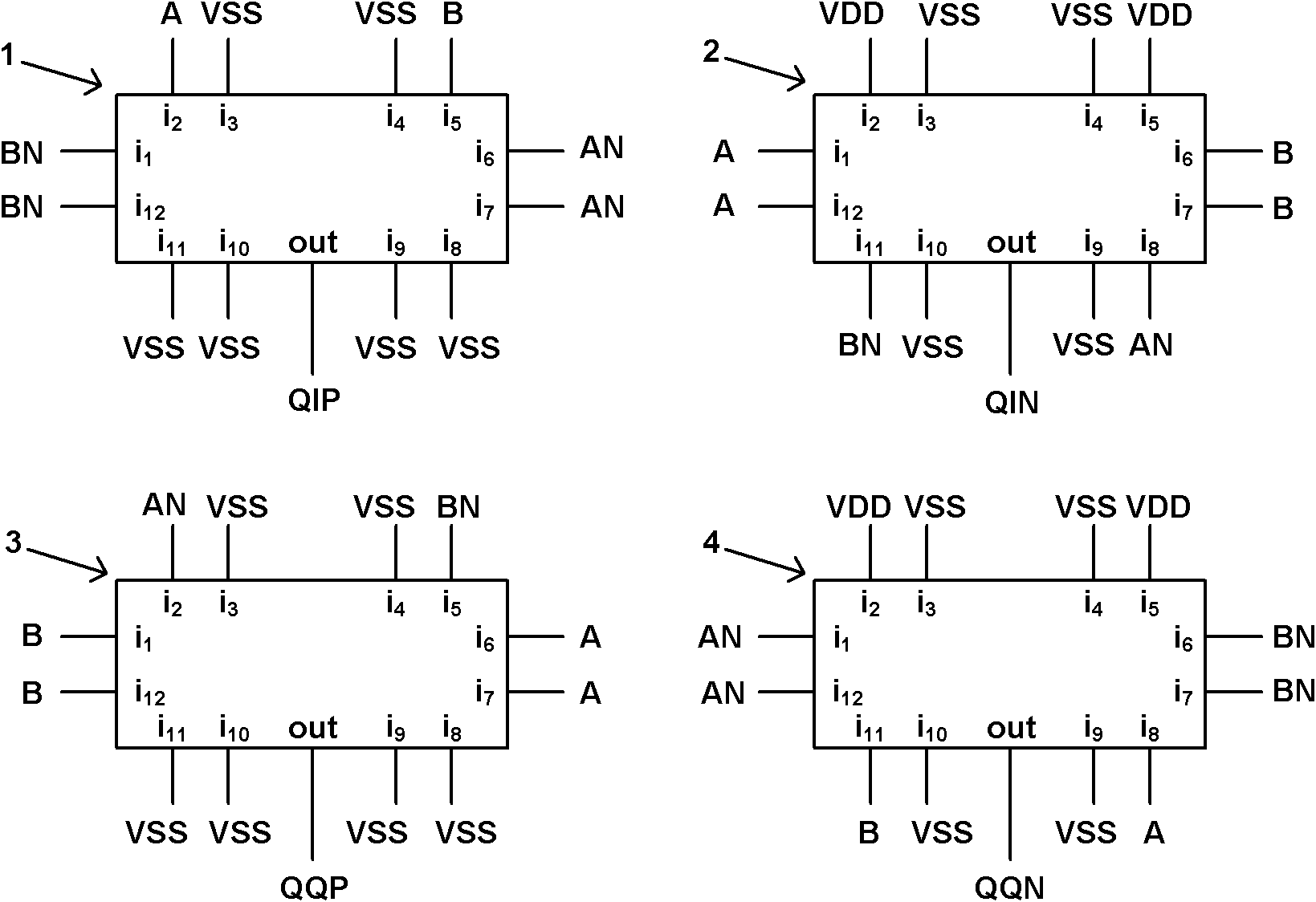

[0025] The ultra-low voltage NAND gate circuit of the present invention is described in detail in conjunction with the drawings and embodiments as follows:

[0026] An ultra-low voltage NAND gate circuit proposed by the present invention, such as figure 2 As shown, it is characterized in that a single-ended input single-ended output structure is adopted, which is composed of a first ultra-low voltage NAND gate basic unit 1 and a second ultra-low voltage NAND gate basic unit 2; The first input terminal i of unit 1 1 Connect to input A, second input i 2 Connect to input B, the third input i 3 Ground voltage VSS, the fourth input terminal i 4 Ground voltage VSS, fifth input terminal i 5 Connect to the power supply voltage VDD, the sixth input terminal i 6 Connect to input A, the seventh input i 7 Connect to input A, the eighth input i 8 Ground voltage VSS, ninth input terminal i 9 Ground voltage VSS, tenth input terminal i 10 Ground voltage VSS, the eleventh input terminal i 11 Conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com