Chaotic discrete particle swarm optimization-based network on chip mapping method

A technique of discrete particle swarm optimization and particle swarm optimization, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems that are not suitable for solving discrete space search problems, and achieve fast convergence speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

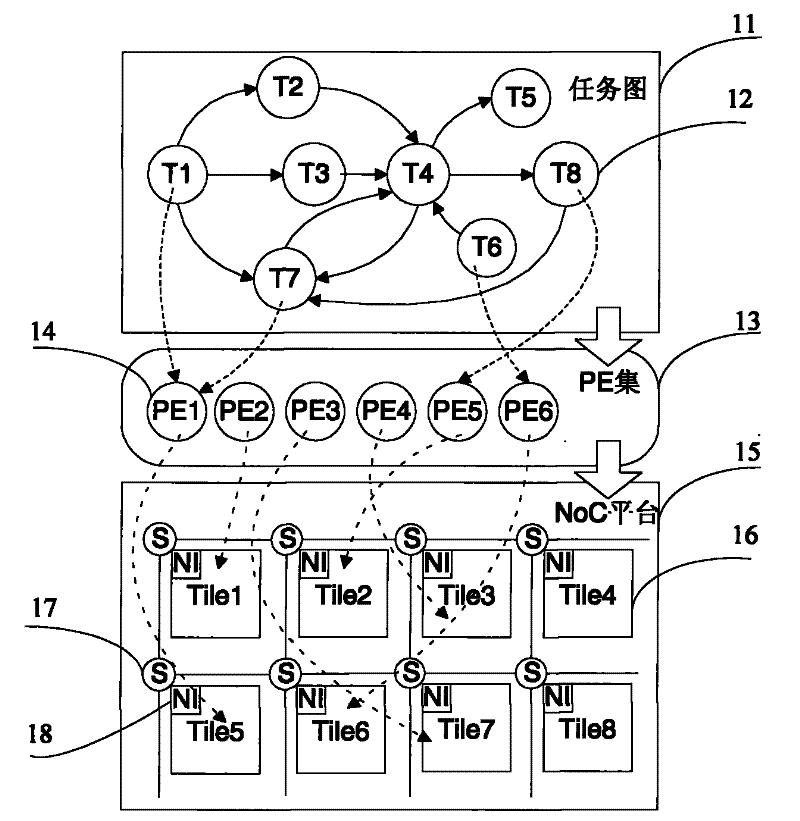

[0061] The specific implementation of the power consumption and delay-oriented NoC mapping scheme search algorithm based on the discrete chaotic particle swarm optimization algorithm in the present invention is introduced below.

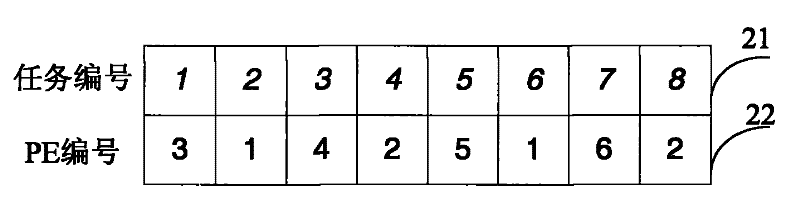

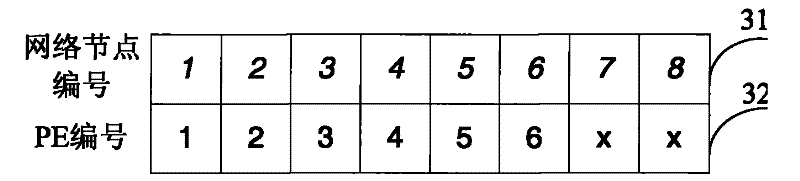

[0062] The mapping process includes two stages: PE selection and network node allocation, such as figure 1 shown. In the first stage, according to the power consumption delay data of tasks on heterogeneous PEs and the average network delay and average power consumption data, the optimal PE selection scheme is obtained by the chaotic discrete particle swarm algorithm. At this time, the high-level application includes a total of 8 tasks: T1-T8, and 6 available PE resources: PE1-PE6. In the second stage, based on the results of the first stage, the chaotic discrete particle swarm algorithm is used to obtain the final mapping result from the PE to the NoC network platform using accurate delay and power consumption parameters.

[0063] The first stage o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com